Motorola DSP56301 User Manual

Page 146

HI32 DSP-Side Programming Model

6

-28

DSP56301 User’s Manual

19

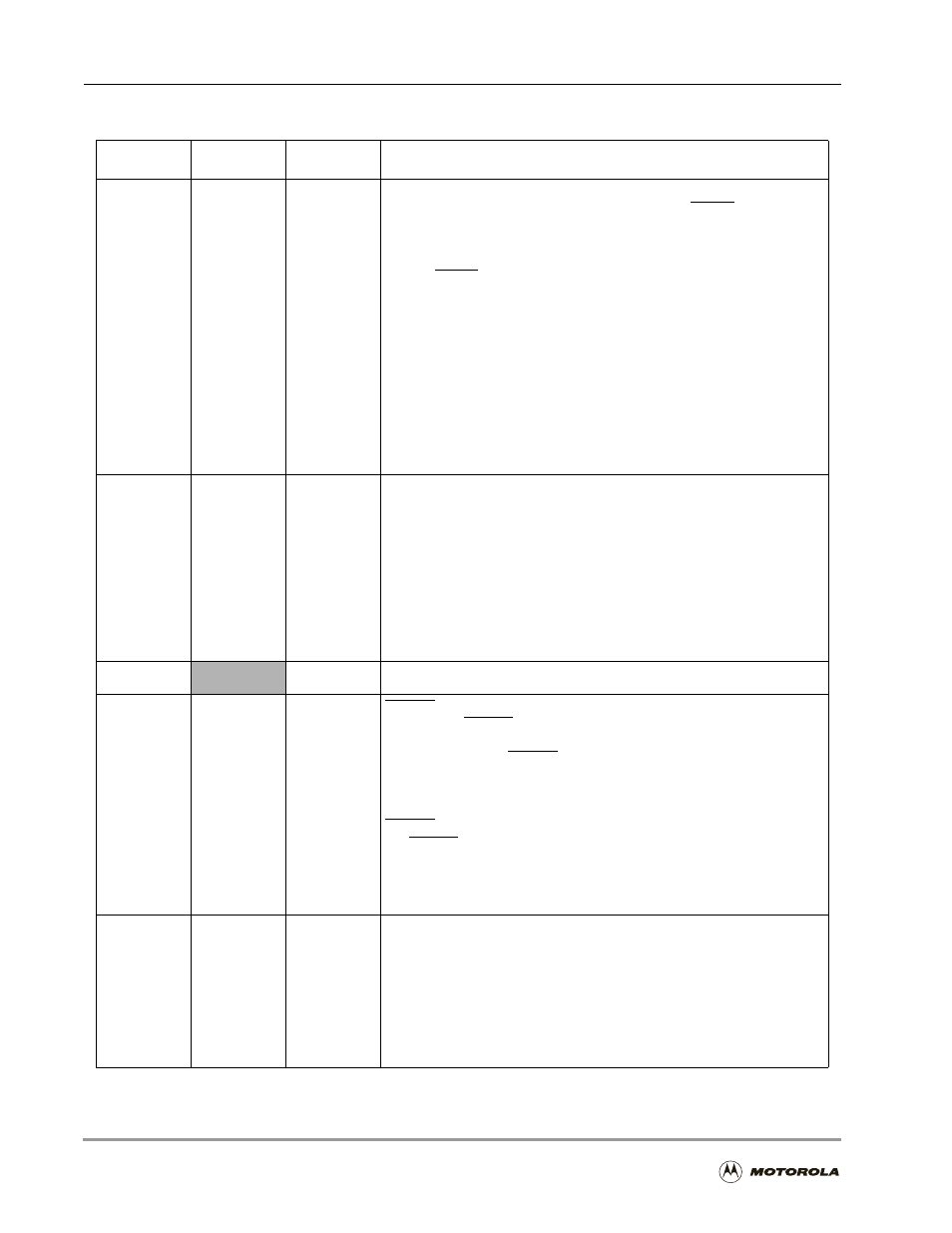

MWSD

0

Master Wait State Disable

Disables PCI wait states (inserted by deasserting HIRDY) during a data

phase. When MWSD is cleared, the HI32 as the active PCI master

(DCTR[HM]

=

$1) inserts wait states to extend the current data phase if

it cannot guarantee the completion of the next data phase. The HI32

asserts HIRDY and completes the current data phase when one of the

following is true:

n

it can complete the next data phase

n

it determines to terminate the transaction due to time-out or

completion

If MWSD is set, the HI32, as the active PCI master (DCTR[HM]

=

$1),

does not insert wait states. If it cannot guarantee the completion of the

next data phase, the HI32 completes the current data phase and

terminates the transaction. MWSD is ignored when the HI32 is not in

the PCI mode (DCTR[HM]

≠

$1). The value of MWSD can change only

when DSR[HACT] = 0.

18

MACE

0

Master Access Counter Enable

Enables/disables the master access counter. When the master access

counter is enabled, the HI32, as the active PCI master (DCTR[HM]

=

$1), terminates the current PCI transaction when the counter reaches

the terminal count. When MACE is cleared, the counter is disabled and

the burst length of HI32-initiated transactions is unlimited. To terminate

an HI32-initiated transaction, the DSP56300 core writes a value of one

to the DPCR[MTT] bit. MACE is ignored when the HI32 is not in PCI

mode (DCTR[HM]

≠

$1). The value of MACE can change only if MARQ =

1 or DSR[HACT] = 0.

17

0

Reserved. Write to 0 for future compatibility.

16

SERF

0

HSERR Force

Controls the HSERR pin state in PCI mode (DCTR[HM]

=

$1). When the

core sets SERF and the HI32 is the current PCI bus master or a

selected target, the HSERR pin is pulsed one PCI clock cycle. If the

system error enable (SERE) bit is set in the Status/Command

Configuration Register (CSTR/CCMR), the signalled system error

(SSE) bit is set in the CSTR/CCMR. HI32 hardware clears SERF after

HSERR is asserted. When SERF is cleared, HI32 hardware controls

the HSERR pin. The DSP56300 core cannot write a value of zero to

SERF. SERF is ignored when the SERE bit is cleared or when the HI32

is not an active PCI agent (that is, DCTR[HM]

≠

$1 or the HI32 is not the

current PCI bus master or a selected target).

15

MTT

0

Master Transfer Terminate

Generates a transaction termination initiated by the PCI master. In PCI

mode (DCTR[HM]

=

$1), when the HI32 is the active PCI master and

the DSP56300 core sets the MT bit, a master- initiated transaction

termination (not master-abort) is generated. HI32 hardware clears MTT

when the PCI bus is in the idle state. The DSP56300 core cannot write

a value of zero to MTT. MTT is ignored when the HI32 is not in the PCI

mode (DCTR[HM]

≠

$1).

Table 6-11. DSP PCI Control Register (DPCR) Bit Definitions (Continued)

Bit Number

Bit Name

Reset Value

Description