7 dsp receive data fifo (drxr), Dsp receive data fifo (drxr) -41, 7 dsp receive data fifo (drxr) – Motorola DSP56301 User Manual

Page 159

HI32 DSP-Side Programming Model

Host Interface (HI32)

6

-41

6.7.7

DSP Receive Data FIFO (DRXR)

The 24-bit wide DSP Receive Data Register (DRXR) is the output stage of the host-to-DSP

data path FIFO for host-to-DSP data transfers (refer to Section 6.3, Data Transfer Paths, on

page 6-6). The DRXR contains master data, that is, data read by the HI32 as PCI master from

an external target to be read if DPSR[MRRQ] is set. MRRQ is cleared if the data in the

DRXR is slave data or when the host-to-DSP data path FIFO is emptied by DSP56300 core

reads. The DSP56300 core can set the DPCR[MRIE] bit to cause a host receive data interrupt

when MRRQ is set.

The DRXR contains slave data—that is, data written to the HI32 from the host bus—to be

read if DSR[SRRQ] is set. DSR[SRRQ] is cleared if the data in the DRXR is master data or

3

0

Reserved. Write to 0 for future compatibility.

2

MRRQ

0

PCI Master Receive Data Request

Indicates that the DSP receive data FIFO (DRXR) contains data read from

the host bus by the HI32 master. When the HI32, as master, reads data

from the host bus to the host-to-DSP FIFO (HTXR-DRXR), MRRQ is set.

MRRQ is cleared if the DRXR is emptied by DSP56300 core reads or the

data to be read from the DRXR is slave data. When MRRQ is set and

DPCR[MRIE] is set, a master receive data interrupt request is generated.

When MRRQ is set and when enabled by an DSP56300 core DMA

channel, a master receive data DMA request is generated. Hardware,

software and personal software resets clear MRRQ.

1

MTRQ

1

PCI Master Transmit Data Request

Indicates that the DSP master transmit data FIFO (DTXM) is not full and

can be written by the DSP56300 core. MTRQ is cleared when the DTXM

is filled by core writes. MTRQ is set when data is output from the

DTXM-HRXM FIFO to the host bus. When MTRQ is set and DPCR[MTIE]

is set, a master transmit data interrupt request is generated. When

enabled by a DSP56300 core DMA channel, a master transmit data DMA

request is generated. Hardware, software, and personal software resets

set MTRQ. In the personal software reset state MTRQ = 0.

0

MWS

0

PCI Master Wait States

Indicates that the HI32, as master in a PCI transaction, inserts wait states

to extend the current data phase (or the first data phase if the transaction

is not yet initiated) by deasserting HIRDY because it cannot guarantee

completion of the next data phase. MWS is enabled when the

DPCR[MWSD] bit is cleared. MWS is set in a PCI write transaction when

there is only one word in the HI32-to-host data path. MWS is set in a PCI

read transaction, if there is only one empty location in the host-to-DSP

data path. This has many applications. For example, the Master Transfer

Terminate (MTT) bit in the DSP PCI Control Register (DPCR) generates a

transaction termination initiated by the PCI master. The DSP56300 core

can set MTT when MWS is set to terminate a transaction after the transfer

of a specific number of words. After MTT is set the HI32 completes the

data phase and terminates the transaction. Hardware, software, and

personal software resets clear MWS.

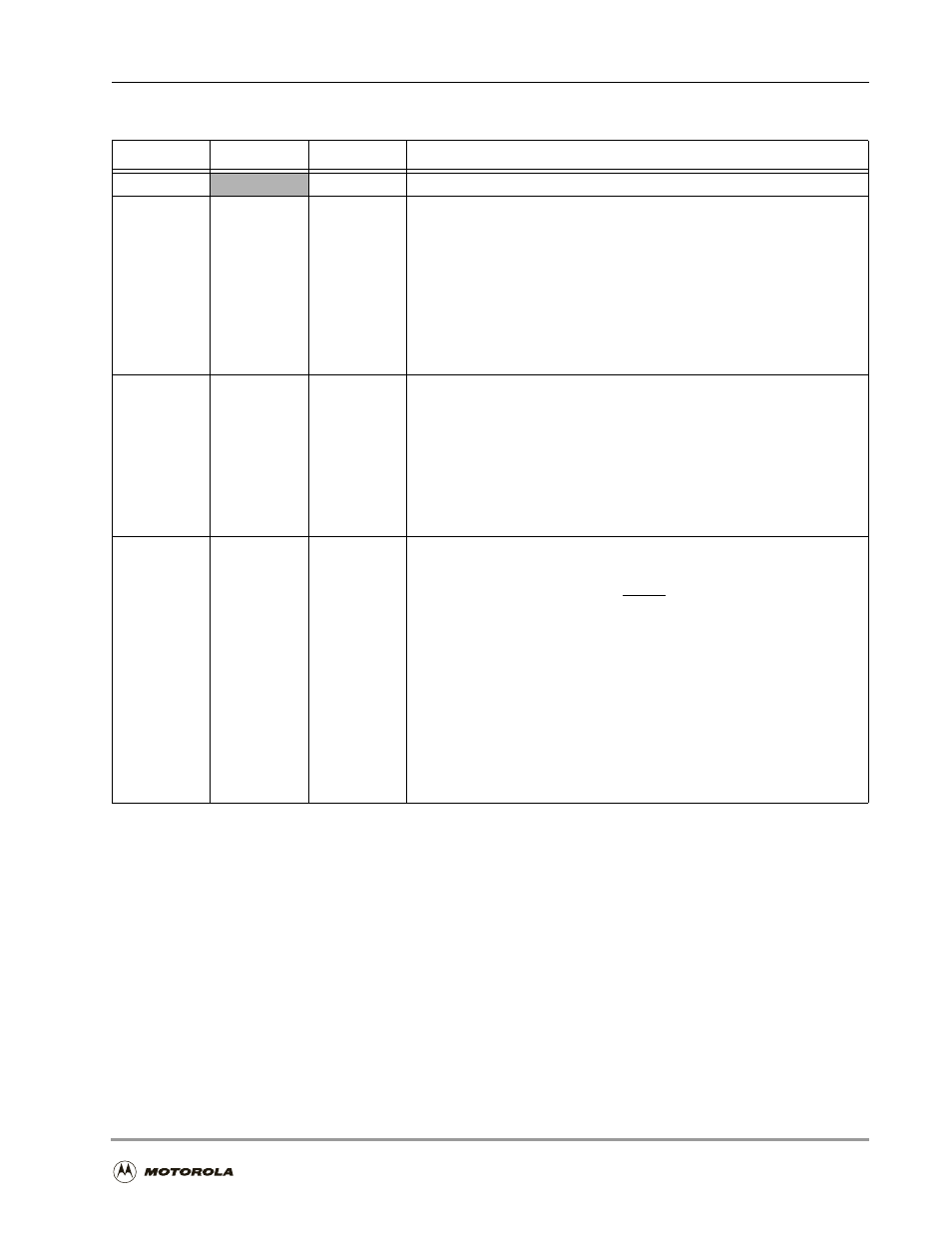

Table 6-15. DSP PCI Status Register (DPSR) Bit Definitions (Continued)

Bit Number

Bit Name

Reset Value

Description