Motorola DSP56301 User Manual

Page 317

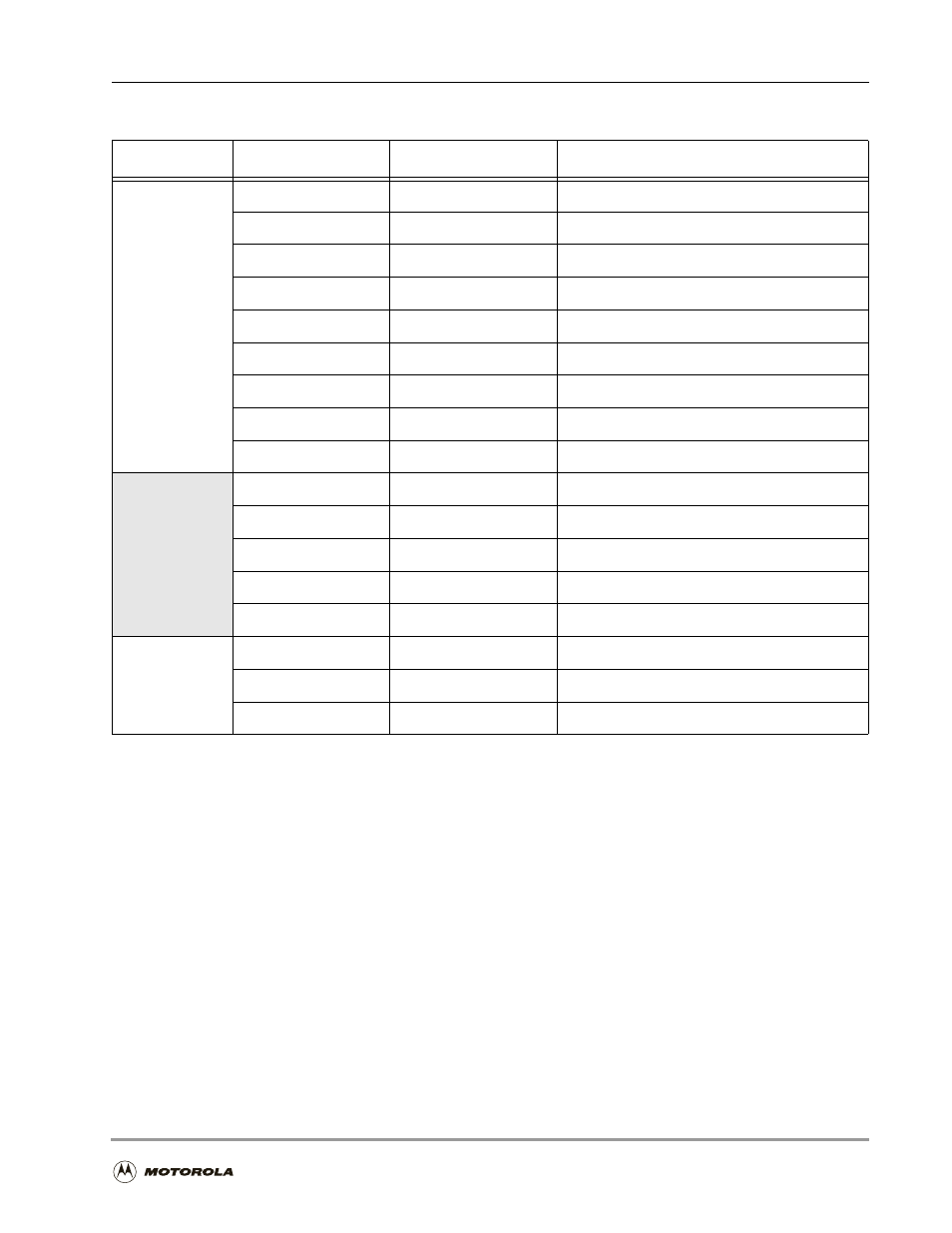

Internal I/O Memory Map

Programming Reference

B

-5

HI32

$FFCD

$FFFFCD

DSP Slave Transmit Data FIFO (DTXS)

$FFCC

$FFFFCC

DSP Master Transmit DATA FIFO (DTXM)

$FFCB

$FFFFCB

DSP Receive Data FIFO (DRXR)

$FFCA

$FFFFCA

DSP PCI Status Register (DPSR)

$FFC9

$FFFFC9

DSP Status Register (DSR)

$FFC8

$FFFFC8

DSP PCI Address Register (DPAR)

$FFC7

$FFFFC7

DSP PCI Master Control Register (DPMC)

$FFC6

$FFFFC6

DSP PCI Control Register (DPCR)

$FFC6

$FFFFC5

DSP Control Register (DCTR)

$FFC4

$FFFFC4

Reserved

$FFC3

$FFFFC3

Reserved

$FFC2

$FFFFC2

Reserved

$FFC1

$FFFFC1

Reserved

$FFC0

$FFFFC0

Reserved

PORT C

$FFBF

$FFFFBF

Port C Control Register (PCRC)

$FFBE

$FFFFBE

Port C Direction Register (PRRC)

$FFBD

$FFFFBD

Port C GPIO Data Register (PDRC)

Table B-2. Internal I/O Memory Map (X Data Memory) (Continued)

Peripheral

16-Bit Address

24-Bit Address

Register Name