Table b-1, Table b-1. guide to programming sheets – Motorola DSP56301 User Manual

Page 314

B

-2

DSP56301 User’s Manual

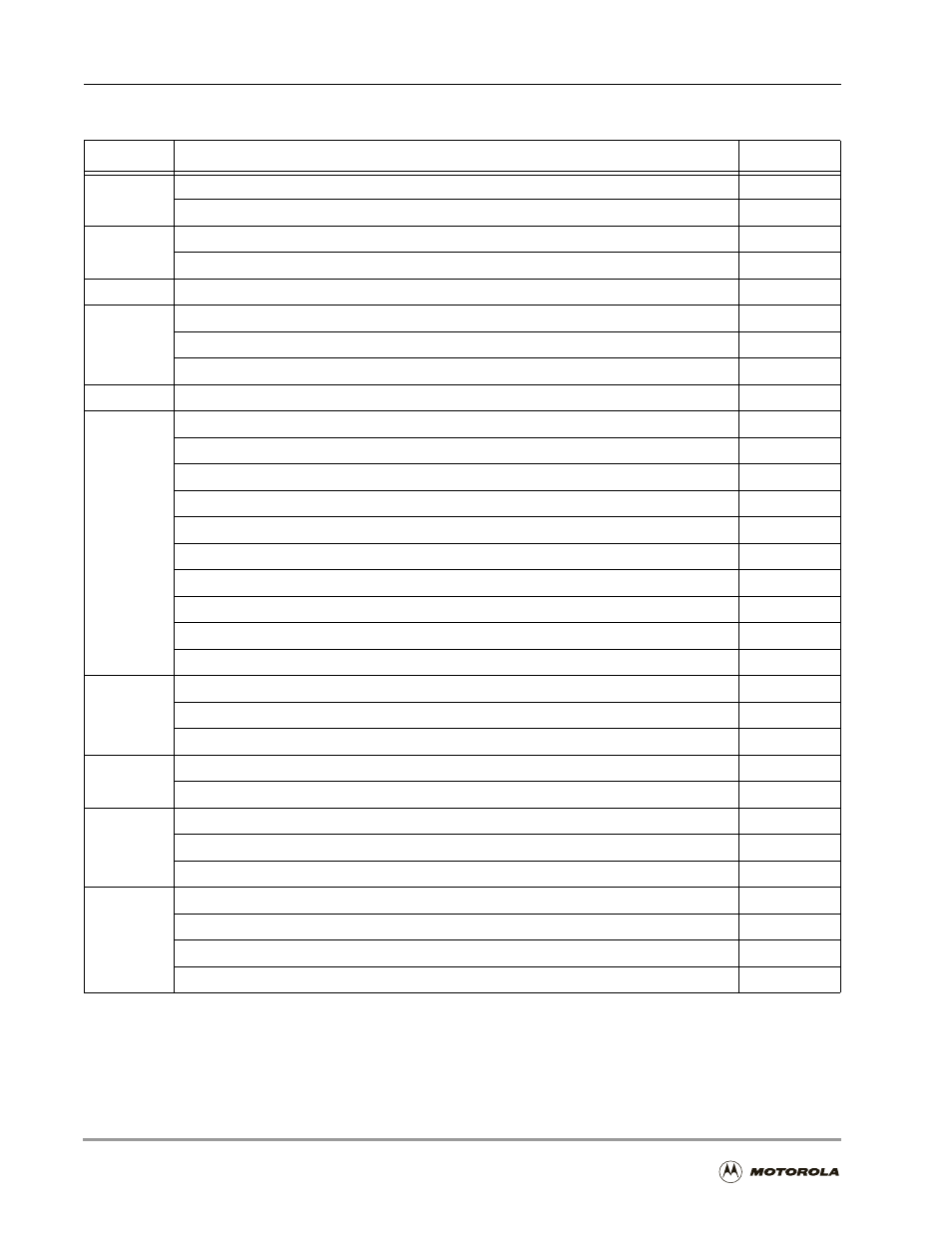

Table B-1. Guide to Programming Sheets

Module

Programming Sheet

Page

Central

Processor

IPR

Interrupt Priority Register Core (IPRC)

Interrupt Priority Register Peripherals (IPRP)

PLL

Phase-Locked Loop Control Register (PCTL)

BIU

Address Attribute Registers (AAR[3–0])

DMA

DMA Control Registers 5–0 (DCR[5–0])

HI32

DSP PCI Control Register (DPCR)

DSP PCI Master Control Register (DPMC)

DSP PCI Address Register (DPAR)

Host Command Vector Register (HCVR)

Status/Command Configuration Register (CSTR/CCMR)

Header Type/Latency Timer Configuration Register (CHTY/CLAT/CCLS)

Memory Space Base Address Configuration Register (CBMA)

Subsystem ID and Subsystem Vendor ID Configuration Register (CSID)

ESSI

ESSI Transmit and Receive Slot Mask Registers (TSM, RSM)

SCI

SCI Clock Control Registers (SCCR)

Timers

Timer Prescaler Load Register (TPLR)

Timer Control/Status Register (TCSR)

GPIO

Host Data Direction and Host Data Registers (HDDR, HDR)

Port C Registers (PCRC, PRRC, PDRC)

Port D Registers (PCRD, PRRD, PDRD)