Essi control register b (crb) bit definitions -19, Signal or a software reset instruction – Motorola DSP56301 User Manual

Page 217

ESSI Programming Model

Enhanced Synchronous Serial Interface (ESSI)

7

-19

Enable (TEIE) bits. In Network mode, if you clear the appropriate TE bit and set it again, then

you disable the corresponding transmitter (0, 1, or 2) after transmission of the current data

word. The transmitter remains disabled until the beginning of the next frame. During that time

period, the corresponding SC (or

STD

in the case of TX0) signal remains in a high-impedance

state. The CRB bits are cleared by either a hardware

RESET

signal or a software RESET

instruction.

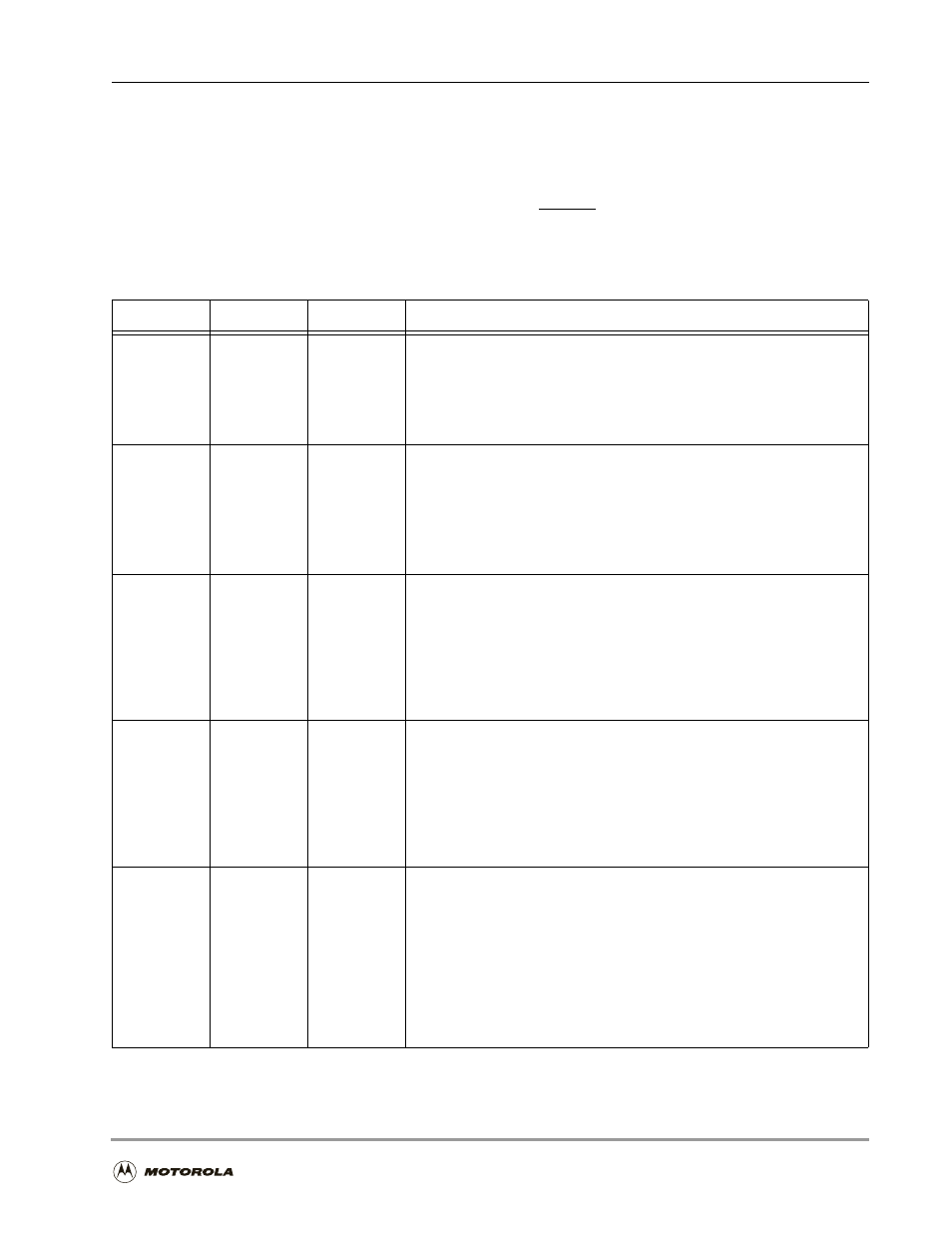

Table 7-4. ESSI Control Register B (CRB) Bit Definitions

Bit Number

Bit Name

Reset Value

Description

23

REIE

0

Receive Exception Interrupt Enable

When the REIE bit is set, the DSP is interrupted when both RDF and ROE

in the ESSI status register are set. When REIE is cleared, this interrupt is

disabled. The receive interrupt is documented in Section 7.3.3,

Exceptions, on page 7-7. A read of the status register followed by a read

of the receive data register clears both ROE and the pending interrupt.

22

TEIE

0

Transmit Exception Interrupt Enable

When the TEIE bit is set, the DSP is interrupted when both TDE and TUE

in the ESSI status register are set. When TEIE is cleared, this interrupt is

disabled. The use of the transmit interrupt is documented in Section

7.3.3,

Exceptions, on page 7-7. A read of the status register, followed by

a write to all the data registers of the enabled transmitters, clears both

TUE and the pending interrupt.

21

RLIE

0

Receive Last Slot Interrupt Enable

Enables/disables an interrupt after the last slot of a frame ends when the

ESSI is in Network mode. When RLIE is set, the DSP is interrupted after

the last slot in a frame ends regardless of the receive mask register

setting. When RLIE is cleared, the receive last slot interrupt is disabled.

The use of the receive last slot interrupt is documented in Section 7.3.3,

Exceptions, on page 7-7. RLIE is disabled when the ESSI is in

On-Demand mode (DC = $0).

20

TLIE

0

Transmit Last Slot Interrupt Enable

Enables/disables an interrupt at the beginning of the last slot of a frame

when the ESSI is in Network mode. When TLIE is set, the DSP is

interrupted at the start of the last slot in a frame regardless of the transmit

mask register setting. When TLIE is cleared, the transmit last slot interrupt

is disabled. The transmit last slot interrupt is documented in Section

7.3.3,

Exceptions, on page 7-7. TLIE is disabled when the ESSI is in

On-Demand mode (DC = $0).

19

RIE

0

Receive Interrupt Enable

Enables/disables a DSP receive data interrupt; the interrupt is generated

when both the RIE and receive data register full (RDF) bit (in the SSISR)

are set. When RIE is cleared, this interrupt is disabled. The receive

interrupt is documented in Section 7.3.3,

the receive data register is read, it clears RDF and the pending interrupt.

Receive interrupts with exception have higher priority than normal receive

data interrupts. If the receiver overrun error (ROE) bit is set (signaling that

an exception has occurred) and the REIE bit is set, the ESSI requests an

SSI receive data with exception interrupt from the interrupt controller.