5 external memory expansion port (port a), 1 external address bus, 2 external data bus – Motorola DSP56301 User Manual

Page 36: 3 external bus control, External memory expansion port (port a) -6, External address bus -6, External data bus -6, External bus control -6, External address bus signals -6, External data bus signals -6

External Memory Expansion Port (Port A)

2

-6

DSP56301 User’s Manual

2.5

External Memory Expansion Port (Port A)

When the DSP56301 enters a low-power standby mode (stop or wait), it releases bus

mastership and tri-states the relevant Port A signals:

A[0

–

23]

,

D[0

–

23]

,

AA0

/

RAS0

–

AA3

/

RAS3

,

RD

,

WR

,

BB

,

CAS

,

BCLK

,

BCLK

.

2.5.1

External Address Bus

2.5.2

External Data Bus

.

2.5.3

External Bus Control

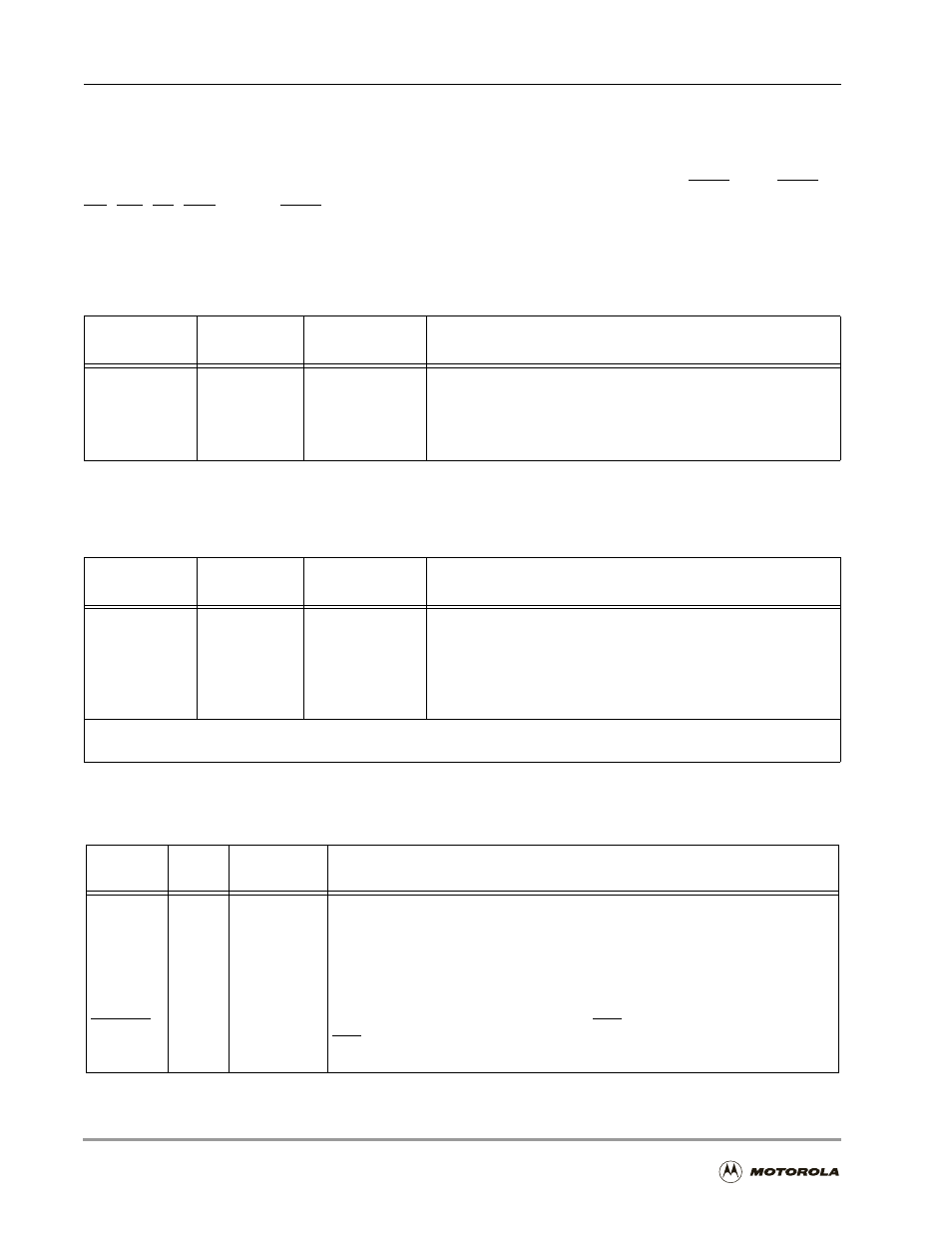

Table 2-6. External Address Bus Signals

Signal Name

Type

State During

Reset

Signal Description

A[0–23]

Output

Tri-stated

Address Bus—When the DSP is the bus master, A[0–23] are

active-high outputs that specify the address for external program

and data memory accesses. Otherwise, the signals are tri-stated.

To minimize power dissipation, A[0–23] do not change state

when external memory spaces are not being accessed.

Table 2-7. External Data Bus Signals

Signal Name

Type

State During

Reset

Signal Description

D[0–23]

Input/ Output

Tri-stated

Data Bus—When the DSP is the bus master, D0–D23 are

active-high, bidirectional input/outputs that provide the

bidirectional data bus for external program and data memory

accesses. Otherwise, D[0–23] are tri-stated. These lines have

weak keepers to maintain the last state even if all drivers are

tri-stated.

Notes: 1.

One pin is reserved for use in the expansion port interface and the peripherals interface. Leave this pin

unconnected.

Table 2-8. External Bus Control Signals

Signal

Name

Type

State During

Reset

Signal Description

AA[0–3]

RAS[0–3]

Output

Output

Tri-stated

Tri-stated

Address Attribute—When defined as AA, these signals can be used as chip

selects or additional address lines. The default use defines a priority scheme

under which only one AA signal can be asserted at a time. Setting the AA priority

disable (APD) bit (Bit 14) of the OMR, the priority mechanism is disabled and the

lines can be used together as four external lines that can be decoded externally

into 16 chip select signals.

Row Address Strobe—When defined as RAS, these signals can be used as

RAS for DRAM interface. These signals are tri-statable outputs with

programmable polarity.