Figure b-8, Address attribute registers (aar[3–0]), Bus interface unit – Motorola DSP56301 User Manual

Page 332: Figure b-8. address attribute registers (aar[3–0])

Programming Sheets

B

-20

DSP56301 User’s Manual

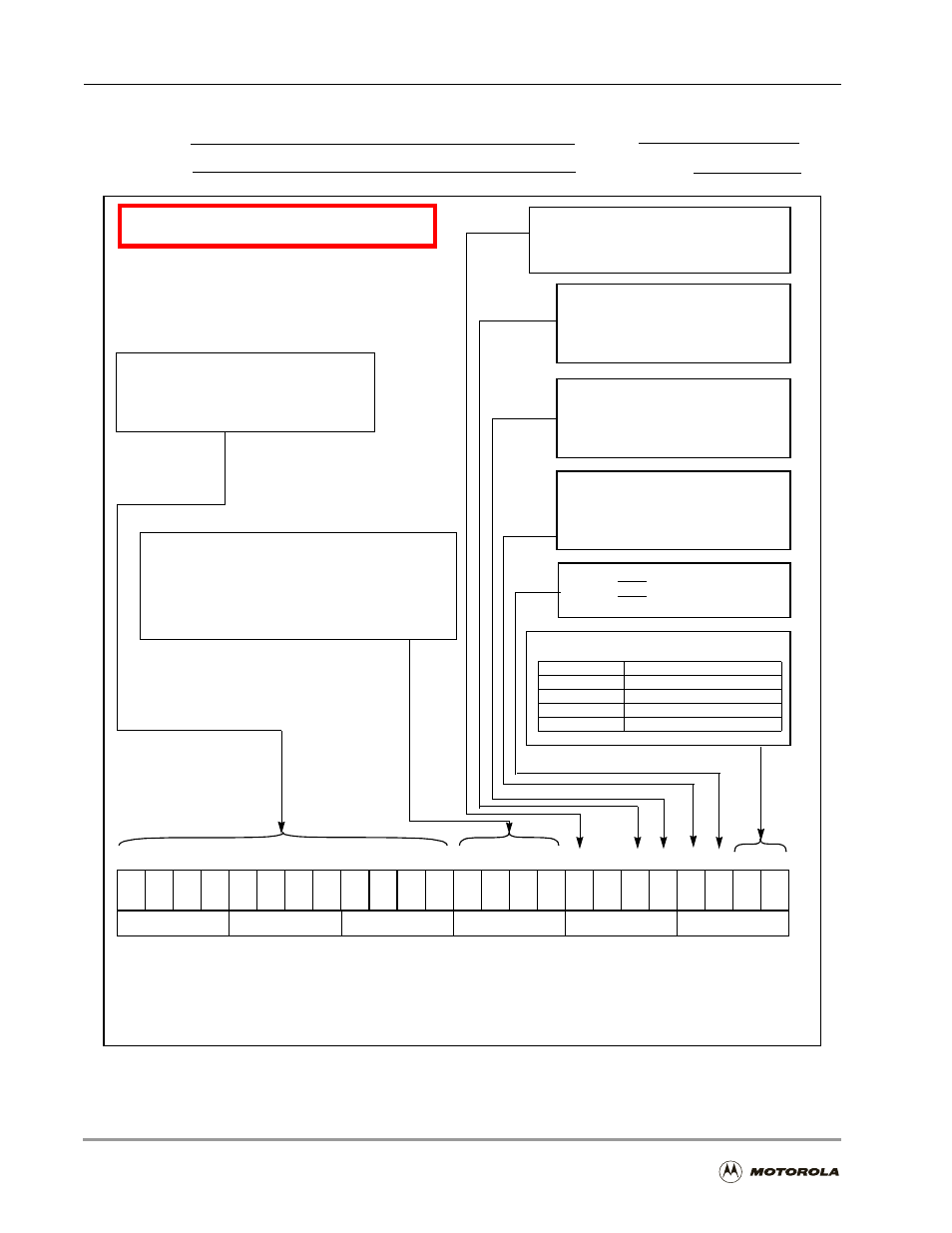

Figure B-8. Address Attribute Registers (AAR[3–0])

Bus Interface Unit

Address Attribute Registers 3 (AAR3)

Reset = $000000

15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

19 18 17 16

23 22 21 20

*

= Reserved, Program as 0

0 = Disable AA pin and logic during

1 = Enable AA pin and logic during

Bus Packing Enable, Bit 7

0 = Disable internal packing/unpacking logic

*

0

Bus Access Type, Bits 1–0

Bus Y Data Memory Enable, Bit 5

1 = Enable internal packing/unpacking logic

Bus Number of Address Bits to Compare, Bits 11–8

BNC[3–0] = number of bits (from BAC bits) that are

Bus Address to Compare, Bits 23–12

BAC[11–0] = address to compare to the

BAC11

(Combinations BNC[3–0] = 1111, 1110, 1101 are

reserved.)

external Y data space accesses

external Y data space accesses

0 = Disable AA pin and logic during

1 = Enable AA pin and logic during

Bus X Data Memory Enable, Bit 4

external X data space accesses

external X data space accesses

0 = Disable AA pin and logic during

1 = Enable AA pin and logic during

Bus Program Memory Enable, Bit 3

external program space accesses

external program space accesses

Bus Address Attribute Polarity, Bit 2

0 =

AA/RAS

signal is active low

1 =

AA/RAS

signal is active high

BAT[1–0]

Encoding

00

Reserved

01

SRAM access

10

DRAM access

11

Reserved

compared to the external address

external address in order to decide

whether to assert the AA pin

Application:

Date:

Programmer:

Sheet 3 of 3

BAC10 BAC9 BAC8 BAC7 BAC6 BAC5 BAC4 BAC3 BAC2 BAC1 BAC0 BNC3 BNC2 BNC1 BNC0 BAC7

BYEN BXEN BPEN BAAP BAT1

BAT0

X:$FFFFF6 Read/Write

Address Attribute Registers 2 (AAR2)

X:$FFFFF7 Read/Write

Address Attribute Registers 1 (AAR1)

X:$FFFFF8 Read/Write

Address Attribute Registers 0 (AAR0)

X:$FFFFF9 Read/Write