Host-side registers (pci memory address space – Motorola DSP56301 User Manual

Page 165

Host-Side Programming Model

Host Interface (HI32)

6

-47

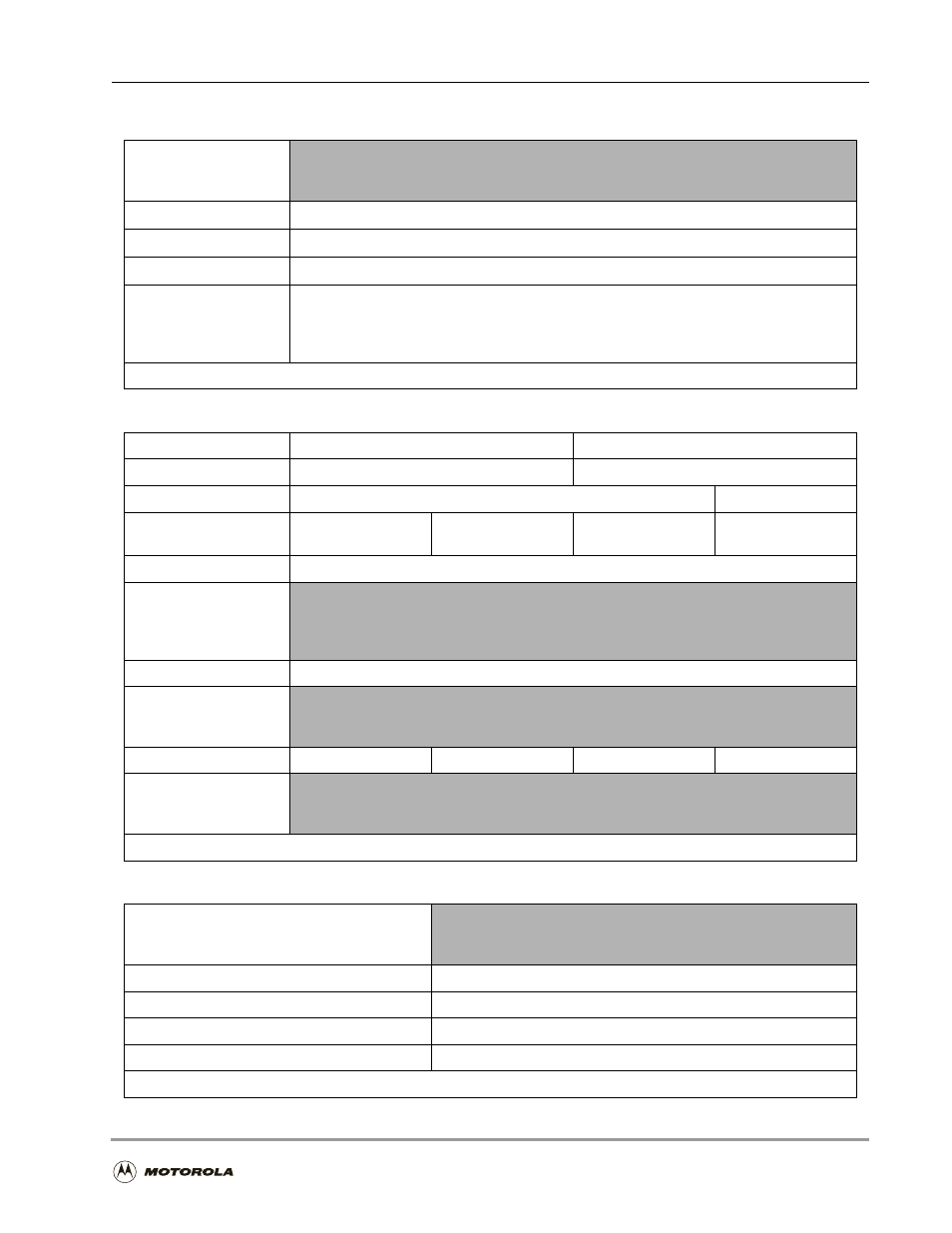

Table 6-19. Host-Side Registers (PCI Memory Address Space

1

)

Base Address: $0000

Base Address:$000C

Reserved

(4 Dwords)

Base Address: $0010

HI32 Control Register (HCTR)

Base Address: $0014

HI32 Status Register (HSTR)

Base Address: $0018

Host Command Vector Register (HCVR)

Base Address:$001C

Base Address:$FFFC

Host Transmit/Slave Receive Data Register (HTXR/HRXS)

(16377 Dwords)

Note:

Addresses are shown in bytes.

Table 6-20. Host-Side Registers (PCI Configuration Address Space

1

)

$00 CDID/CVID

Device ID (CDID)

Vendor ID (CVID)

$04 CSTR/CCMR

Status (CSTR)

Command (CCMR)

$08 CCCR/CRID

Class Code (CCCR)

Revision ID (CRID)

$0C CHTY/CLAT

Header Type

(CHTY)

Latency Timer

(CLAT)

Cache Line (CCLS)

$10 CBMA

Memory Space Base Address (CBMA)

$14

$28

Reserved(6 Dwords)

$2C

CSID

Subsystem ID and Subsystem Vendor ID (CSID)

$30

$38

Reserved

(3 Dwords)

$3C (CILP)

MAX_LAT

MIN_GNT

Interrupt Line

Interrupt Pin

$40

$FC

(48 Dwords)

Note:

Addresses are shown in bytes.

Table 6-21. Host-Side Registers (Universal Bus Mode Address Space

1

)

Base Address: $0

Base Address: $3

Reserved

(4 Locations)

Base Address: $4

HI32 Control Register (HCTR)

Base Address: $5

HI32 Status Register (HSTR)

Base Address: $6

Host Command Vector Register (HCVR)

Base Address: $7

Host Transmit/Slave Receive Data FIFO (HTXR/HRXS)

Note:

Addresses shown are in words (locations). The base address is defined by eight bits of the CBMA register.