B-17, Figure b-17, Host processor (hi32) – Motorola DSP56301 User Manual

Page 341

Programming Sheets

Programming Reference

B

-29

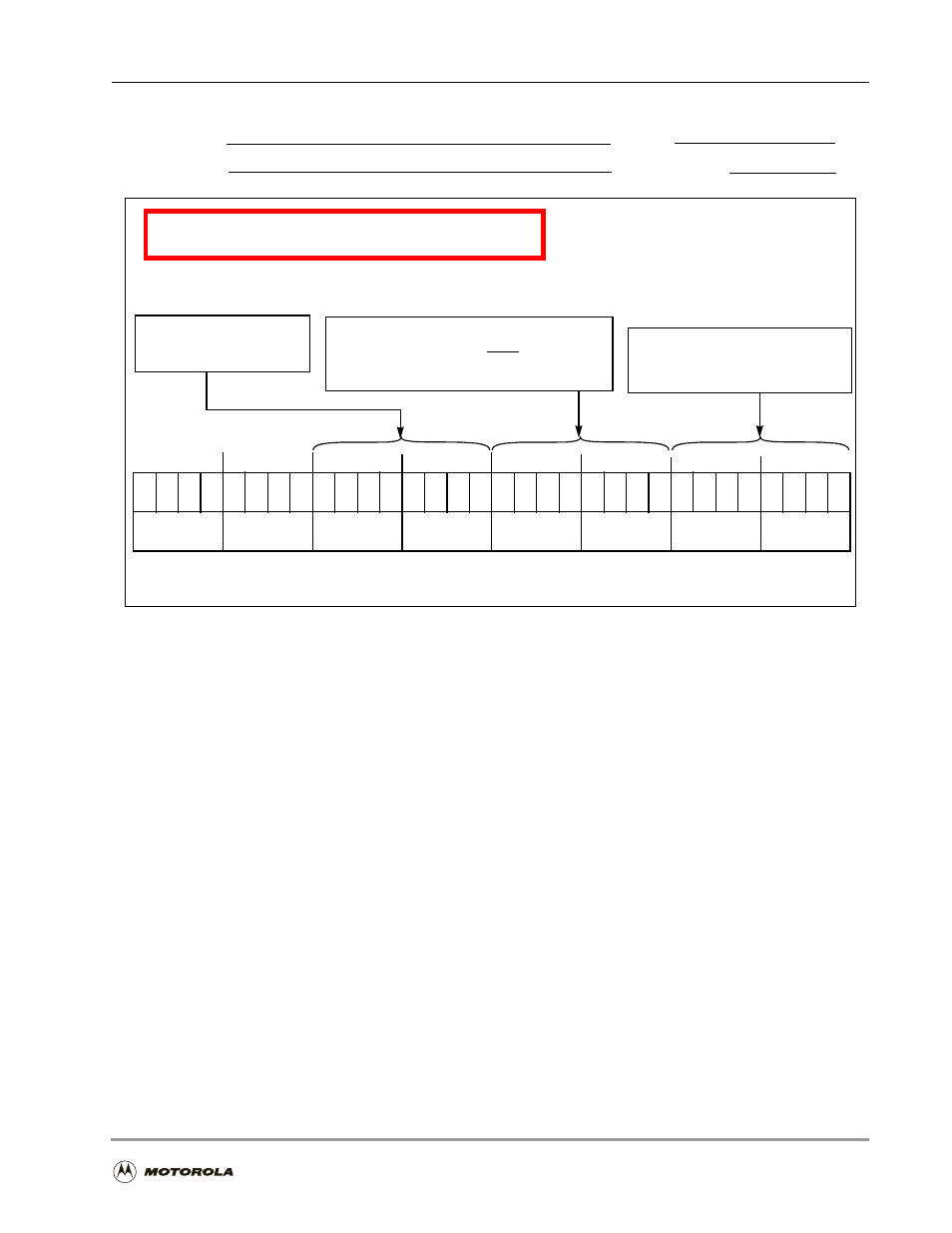

Figure B-17. Header Type/Latency Timer Configuration Register (CHTY/CLAT/CCLS)

Host Processor (HI32)

HI32 Header Type/Latency Timer Configuration Register (CHTY/CLAT/CCLS)

Reset = $00000000

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

0

19 18 17 16

23 22 21 20

Header Type, Bits 23–16

Read-only; hardwired to $00

PCI: Specifies the latency timer in PCI bus cycles

UBM: Specifies duration of HIRQ pulse

Latency Timer (High), Bits 15–8

*

= Reserved, Program as 0

*

0

Read/Write

Application:

Date:

Programmer:

Sheet 8 of 10

27 26 25 24

31 30 29 28

*

0

*

0

*

0

*

0

*

0

*

0

*

0

CLS7 CLS6

CLS5 CLS4 CLS3 CLS2 CLS1

Cache Line Size, Bits 7–0

CCLS Register

Specifies cache line size (32-bit words)

Modes: UBM and PCI

CLS0

Modes: PCI only

Modes: UBM and PCI

HT7

HT6

HT5

HT4

HT3

HT2

HT1

HT0

LT7

LT6

LT5

LT4

LT3

LT2

LT1

LT0

0 0 0 0 0 0 0 0