Motorola DSP56301 User Manual

Page 169

Host-Side Programming Model

Host Interface (HI32)

6

-51

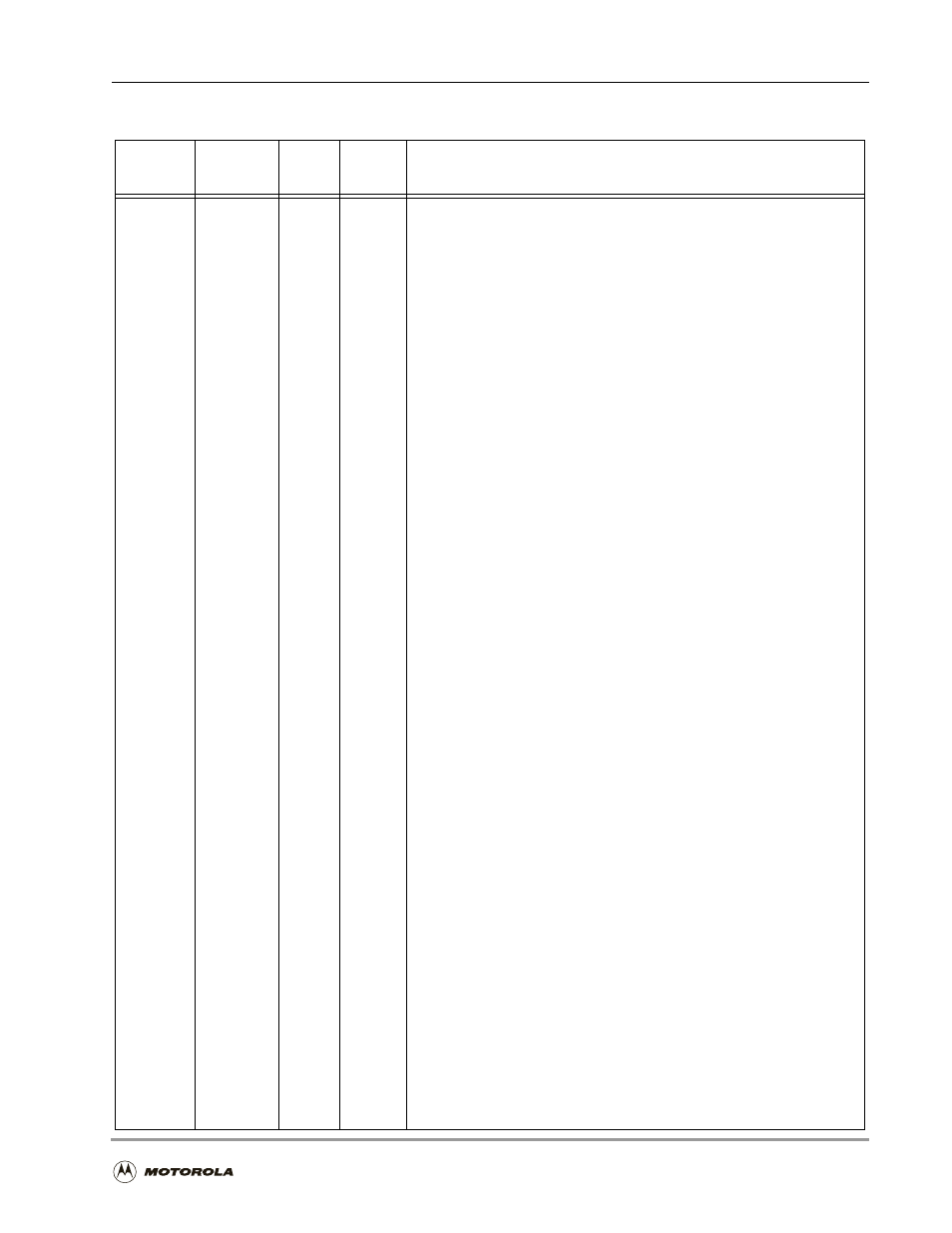

9–8

HTF[1–0]

0

UBM

PCI

Host Transmit Data Transfer Format

Define data transfer formats for host-to-DSP communication. The data

transfer format converter (HDTFC) operates according to the specified

HTF[1–0] (see Table Table 6-4,

Transmit Data Transfer Format, on

page 6-9). The personal hardware reset clears HTF[1–0].

PCI host-t- DSP data transfer formats (DCTR[HM] = $1):

n

If HCTR[HTF] = $0 (32-bit data mode):

All four PCI data bytes from HAD[31–0] pins are written to the

32-bit HTXR. The two least significant bytes are transferred to the

two least significant bytes of the DRXR FIFO. Then the two most

significant bytes are transferred to the two least significant bytes of

the DRXR FIFO. Thus, when the DSP56300 core reads two words

from the DRXR, the two least significant bytes of the first word read

contain the two least significant bytes of the 32-bit word written to

the HTXR, the two least significant bytes of the second word read

contain the two most significant bytes of the 32-bit word.

n

If HCTR[HTF] = $1 or $2:

The three least significant PCI data bytes from the HAD[23–0] pins

transfer to the three least significant HTXR bytes and are sent to

DRXR to be read by the DSP56300 core.

n

If HCTR[HTF] = $3:

The three most significant PCI data bytes from the HAD[31–8] pins

transfer to the three least significant HTXR bytes and are sent to

the DRXR to be read by the DSP56300 core.

Universal Bus mode host-to-DSP data transfer formats (DCTR[HM] = $2

or $3):

n

If HCTR[HTF] = $0:

The 24-bit data from HD[23–0] data pins transfers to the three least

significant HTXR bytes and is sent to DRXR to be read by the

DSP56300 core.

n

If HCTR[HTF] = $1:

The 16-bit data from HD[15–0] data pins transfers to the three least

significant HTXR bytes as right aligned and zero extended and

sent to DRXR to be read by the DSP56300 core.

n

If HCTR[HTF] = $2:

The 16-bit data from HD[15–0] data pins transfers to the three least

significant HTXR bytes as right aligned and sign extended and

sent to DRXR to be read by the DSP56300 core.

n

If HCTR[HTF] = $3:

The 16-bit data from HD[15–0] data pins transfers to the three least

significant bytes of the HTXR as left aligned. The least significant

byte is zero filled and sent to DRXR to be read by the DSP56300

core.

To assure proper operation:

n

HTF[1–0] can be changed if the host-to-DSP data path is empty.

n

Switching between 32-bit data modes and non-32-bit data modes

can occur only in the personal software reset state (DCTR[HM] =

$0 and HACT = 0).

n

If the HTF[1–0] value is not equal to the value of the FC[1–0] bits in

the DPMC, PCI transactions that start in the non-data address

space (the PCI address is less than HI32_base_address:$007)

should not extend into the data address space.

Table 6-22. Host Interface Control Register (HCTR) Bit Definitions (Continued)

Bit

Number

Bit Name

Reset

Value

Mode

Description