Motorola DSP56301 User Manual

Page 249

SCI Programming Model

Serial Communication Interface (SCI)

8

-13

13

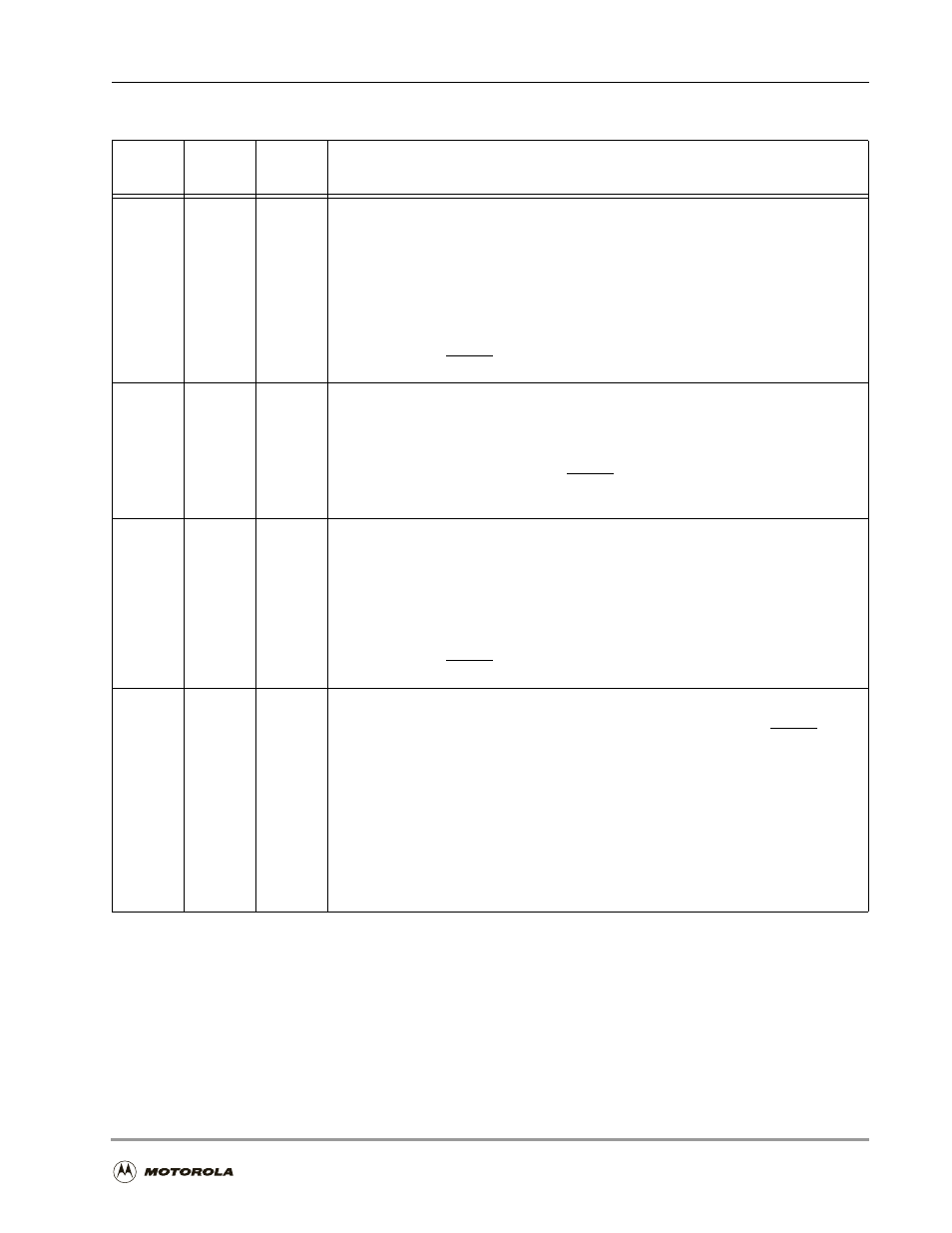

TMIE

0

Timer Interrupt Enable

Enables/disables the SCI timer interrupt. If TMIE is set, timer interrupt requests are

sent to the interrupt controller at the rate set by the SCI clock register. The timer

interrupt is automatically cleared by the timer interrupt acknowledge from the interrupt

controller. This feature allows DSP programmers to use the SCI baud rate generator as

a simple periodic interrupt generator if the SCI is not in use, if external clocks are used

for the SCI, or if periodic interrupts are needed at the SCI baud rate. The SCI internal

clock is divided by 16 (to match the 1

×

SCI baud rate) for timer interrupt generation.

This timer does not require that any SCI signals be configured for SCI use to operate.

Either a hardware RESET signal or a software RESET instruction clears TMIE.

12

TIE

0

SCI Transmit Interrupt Enable

Enables/disables the SCI transmit data interrupt. If TIE is cleared, transmit data

interrupts are disabled, and the transmit data register empty (TDRE) bit in the SCI

status register must be polled to determine whether the transmit data register is empty.

If both TIE and TDRE are set, the SCI requests an SCI transmit data interrupt from the

interrupt controller. Either a hardware RESET signal or a software RESET instruction

clears TIE.

11

RIE

0

SCI Receive Interrupt Enable

Enables/disables the SCI receive data interrupt. If RIE is cleared, the receive data

interrupt is disabled, and the RDRF bit in the SCI status register must be polled to

determine whether the receive data register is full. If both RIE and RDRF are set, the

SCI requests an SCI receive data interrupt from the interrupt controller. Receive

interrupts with exception have higher priority than normal receive data interrupts.

Therefore, if an exception occurs (that is, if PE, FE, or OR are set) and REIE is set, the

SCI requests an SCI receive data with exception interrupt from the interrupt controller.

Either a hardware RESET signal or a software RESET instruction clears RIE.

10

ILIE

0

Idle Line Interrupt Enable

When ILIE is set, the SCI interrupt occurs when IDLE (SCI status register bit 3) is set.

When ILIE is cleared, the IDLE interrupt is disabled. Either a hardware RESET signal

or a software RESET instruction clears ILIE. An internal flag, the shift register idle

interrupt (SRIINT) flag, is the interrupt request to the interrupt controller. SRIINT is not

directly accessible to the user. When a valid start bit is received, an idle interrupt is

generated if both IDLE and ILIE are set. The idle interrupt acknowledge from the

interrupt controller clears this interrupt request. The idle interrupt is not asserted again

until at least one character has been received. The results are as follows:

n

The IDLE bit shows the real status of the receive line at all times.

n

An idle interrupt is generated once for each idle state, no matter how long the

idle state lasts.

Table 8-2. SCI Control Register (SCR) Bit Definitions (Continued)

Bit

Number

Bit Name

Reset

Value

Description