2 sci status register (ssr), Sci status register (ssr) -17, Sci status register -17 – Motorola DSP56301 User Manual

Page 253: Sci status register (ssr) bit definitions -17, R (ssr) in figure 8-3, 2 sci status register (ssr)

SCI Programming Model

Serial Communication Interface (SCI)

8

-17

8.6.2

SCI Status Register (SSR)

The SSR is a read-only register that indicates the status of the SCI.

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R8

FE

PE

OR

IDLE

RDRF

TDRE

TRNE

—Reserved bit; read as 0; write to 0 for future compatibility.

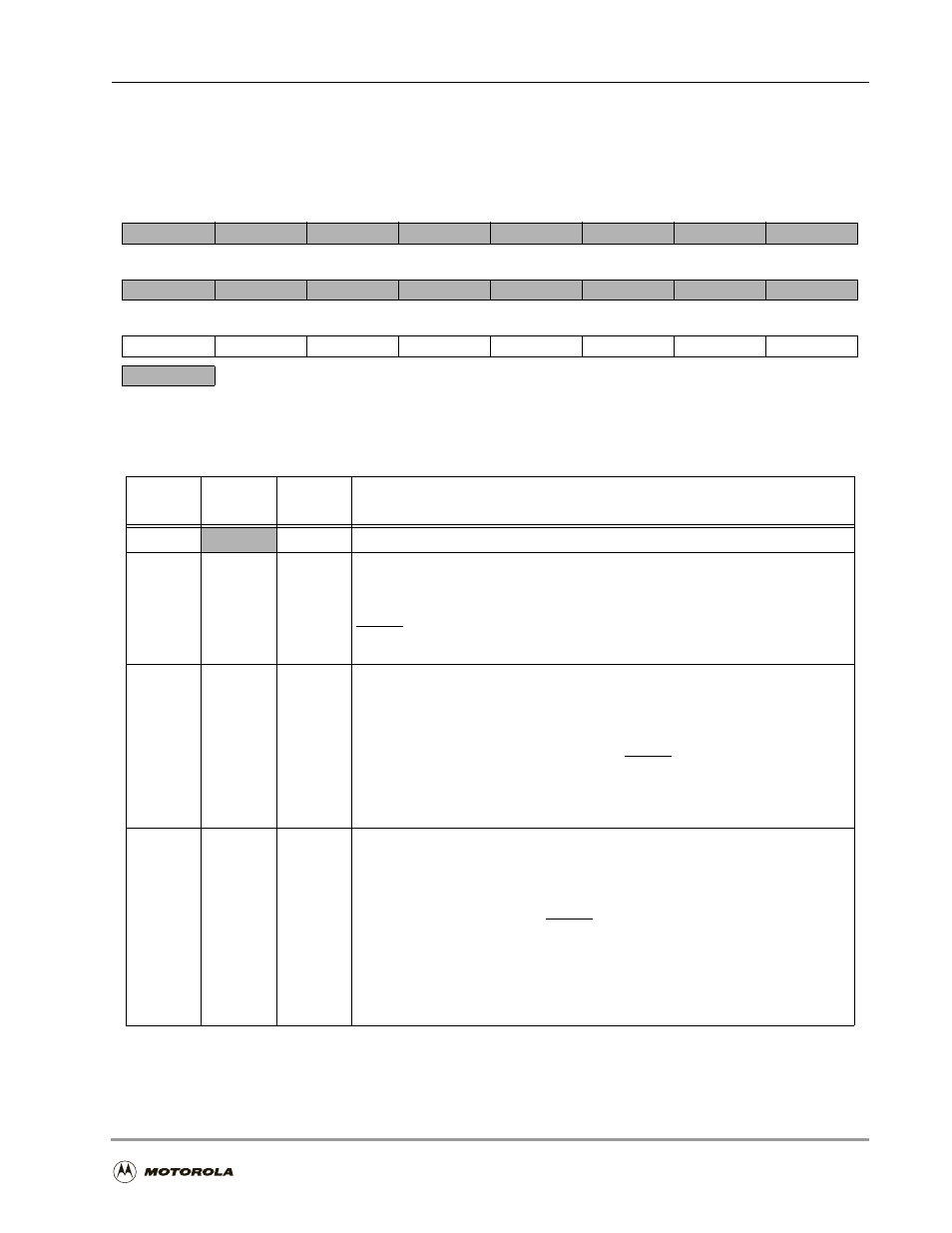

Table 8-3. SCI Status Register

Table 8-4. SCI Status Register (SSR) Bit Definitions

Bit

Number

Bit Name

Reset

Value

Description

23–8

0

Reserved. Write to 0 for future compatibility.

7

R8

0

Received Bit 8

In 11-bit Asynchronous Multidrop mode, the R8 bit indicates whether the

received byte is an address or data. R8 is set for addresses and is cleared for

data. R8 is not affected by reads of the SRX or SCI status register. A hardware

RESET signal, a software RESET instruction, an SCI individual reset, or a STOP

instruction clears R8.

6

FE

0

Framing Error Flag

In Asynchronous mode, FE is set when no stop bit is detected in the data string

received. FE and RDRE are set simultaneously when the received word is

transferred to the SRX. However, the FE flag inhibits further transfer of data into

the SRX until it is cleared. FE is cleared when the SCI status register is read

followed by a read of the SRX. A hardware RESET signal, a software RESET

instruction, an SCI individual reset, or a STOP instruction clears FE. In 8-bit

Synchronous mode, FE is always cleared. If the byte received causes both

framing and overrun errors, the SCI receiver recognizes only the overrun error.

5

PE

0

Parity Error

In 11-bit Asynchronous modes, PE is set when an incorrect parity bit is detected

in the received character. PE and RDRF are set simultaneously when the

received word is transferred to the SRX. If PE is set, further data transfer into the

SRX is not inhibited. PE is cleared when the SCI status register is read, followed

by a read of SRX. A hardware RESET signal, a software RESET instruction, an

SCI individual reset, or a STOP instruction also clears PE. In 10-bit

Asynchronous mode, 11-bit multidrop mode, and 8-bit Synchronous mode, the

PE bit is always cleared since there is no parity bit in these modes. If the byte

received causes both parity and overrun errors, the SCI receiver recognizes only

the overrun error.