8 device identification register (idr), Dsp slave transmit data register (dtxs), 8 device identification register (idr) – Motorola DSP56301 User Manual

Page 108

Device Identification Register (IDR)

4

-34

DSP56301 User’s Manual

4.8

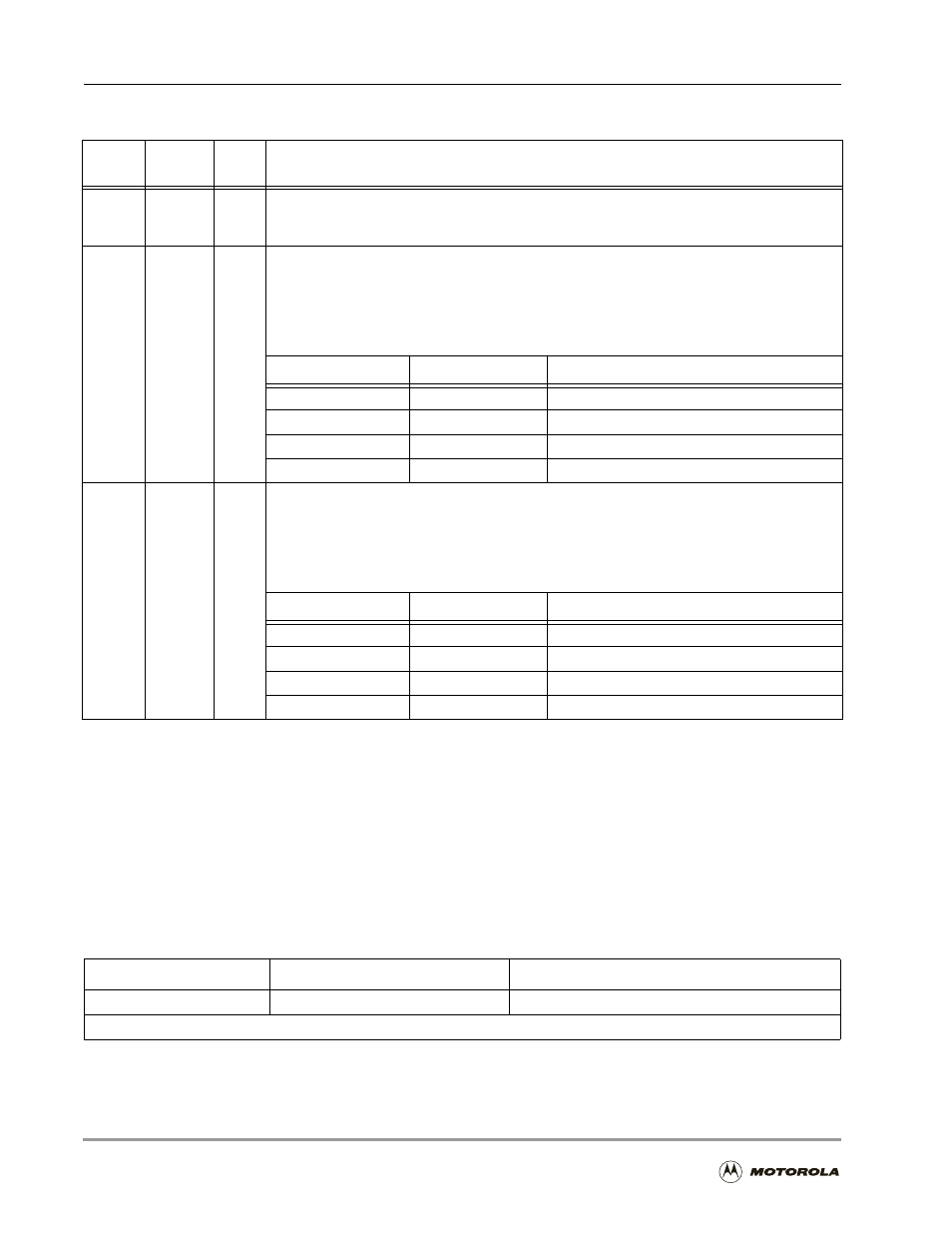

Device Identification Register (IDR)

The IDR is a read-only factory-programmed register that identifies DSP56300 family

members. It specifies the derivative number and revision number of the device. This

information is used in testing or by software. Figure 4-10 shows the contents of the IDR.

Revision numbers are assigned as follows: $0 is revision 0, $1 is revision A, and so on.

.

Figure 4-10. Identification Register Configuration (Revision E)

9–4

DAM[5–0]

0

DMA Address Mode

Defines the address generation mode for the DMA transfer. These bits are encoded in two

different ways according to the D3D bit.

3–2

DDS[1–0]

0

DMA Destination Space

Specify the memory space referenced as a destination by the DMA.

Note:

In Cache mode, a DMA to Program memory space has some limitations (as

described in Chapter 8,

Instruction Cache, and Chapter 11, Operating Modes and

Memory Spaces in the DSP56300 Family Manual).

DDS1

DDS0

DMA Destination Memory Space

0

0

X Memory Space

0

1

Y Memory Space

1

0

P Memory Space

1

1

Reserved

1–0

DSS[1–0]

0

DMA Source Space

Specify the memory space referenced as a source by the DMA.

Note:

In Cache mode, a DMA to Program memory space has some limitations (as

described in Chapter 8,

Instruction Cache, and Chapter 11, Operating Modes and

Memory Spaces in the DSP56300 Family Manual).

DSS1

DSS0

DMA Source Memory Space

0

0

X Memory Space

0

1

Y Memory Space

1

0

P Memory Space

1

1

Reserved

23

16

15

12

11

0

Reserved

Revision Number

Derivative Number

$00

See Note

$301

Note:

No specific revision number is shown because this manual is current for several revisions of the DSP56301.

Table 4-12. DMA Control Register (DCR) Bit Definitions (Continued)

Bit

Number

Bit Name

Reset

Value

Description