Status register (sr) -7, Status register bit definitions -7 – Motorola DSP56301 User Manual

Page 81

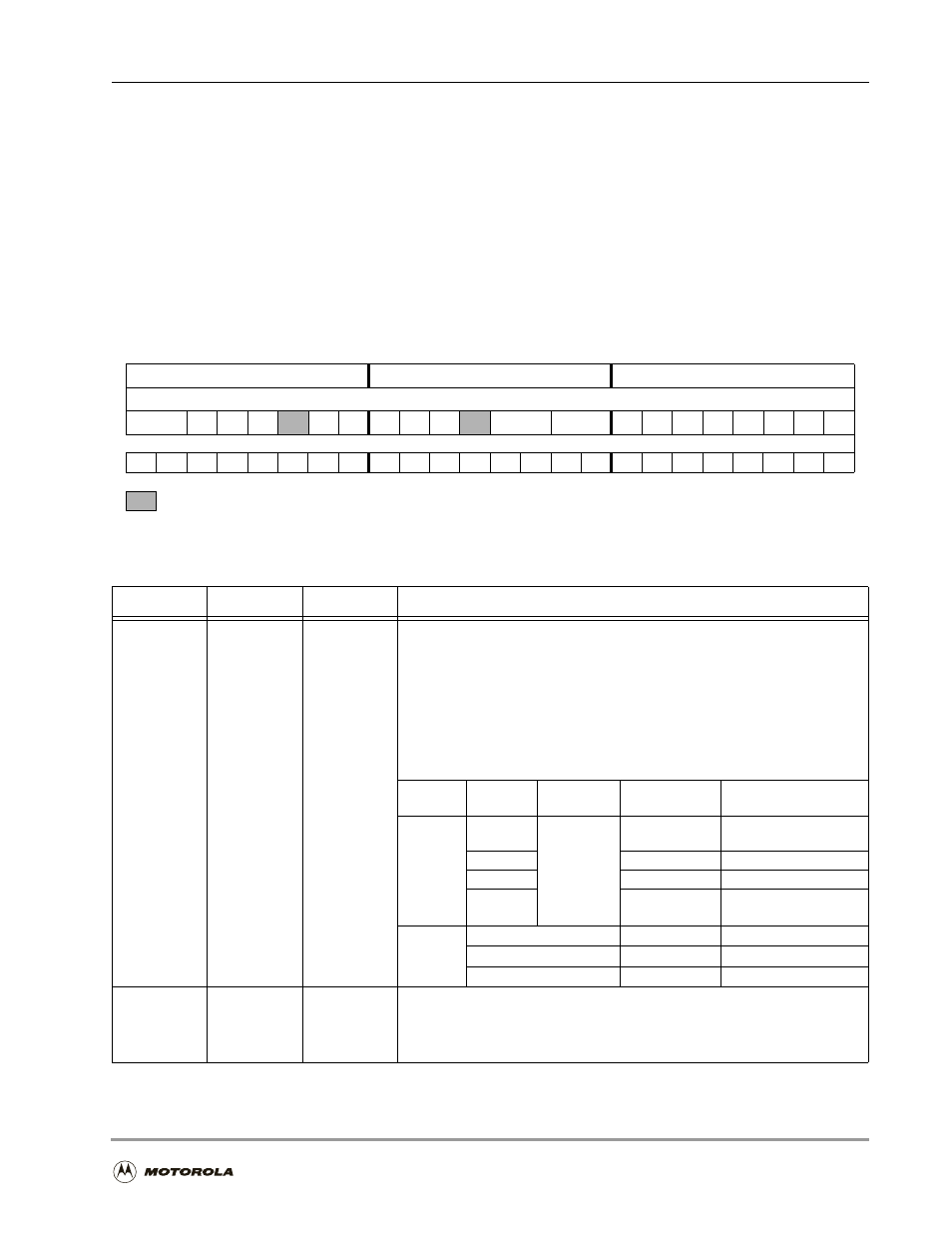

Central Processor Unit (CPU) Registers

Core Configuration

4

-7

n

Condition Code Register (CCR) (SR[7–0])—Defines the results of previous arithmetic

computations. The CCR bits are affected by Data Arithmetic Logic Unit (Data ALU)

operations, parallel move operations, instructions that directly reference the CCR (for

example, ORI and ANDI), and instructions that specify SR as a destination (for

example, MOVEC). Parallel move operations affect only the S and L bits of the CCR.

During processor reset, all CCR bits are cleared.

The definition of the three 8-bit registers within the SR is primarily for the purpose of

compatibility with other Motorola DSPs. Bit definitions in the following paragraphs identify

the bits within the SR and not within the subregister.

Extended Mode Register (EMR)

Mode Register (MR)

Condition Code Register (CCR)

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

CP[1–0] RM SM CE

SA FV

LF DM SC

S[1–0]

I[1–0]

S

L

E

U

N

Z

V

C

Reset:

1

1

0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

0

0

0

Reserved bit. Read as zero; write to zero for future compatibility

Figure 4-1. Status Register (SR)

Table 4-3. Status Register Bit Definitions

Bit Number

Bit Name

Reset Value

Description

23–22

CP[1–0]

11

Core Priority

Under control of the CDP[1–0] bits in the OMR, the CP bits specify the

priority of core accesses to external memory. These bits are compared

against the priority bits of the active DMA channel. If the core priority is

greater than the DMA priority, the DMA waits for a free time slot on the

external bus. If the core priority is less than the DMA priority, the core waits

for a free time slot on the external bus. If the core priority equals the DMA

priority, the core and DMA access the external bus in a round robin pattern

(for example, ... P, X, Y, DMA, P, X, Y, ...).

Priority

Mode

Core

Priority

DMA

Priority

OMR

(CDP[1-0])

SR (CP[1–0])

Dynamic

0

(Lowest)

Determined

by DCRn

(DPR[1–0])

for active

DMA

channel

00

00

1

00

01

2

00

10

3

(Highest)

00

11

Static

core < DMA

01

xx

core = DMA

10

xx

core > DMA

11

xx

21

RM

0

Rounding Mode

Selects the type of rounding performed by the Data ALU during arithmetic

operations. If RM is cleared, convergent rounding is selected. If RM is set,

two’s-complement rounding is selected.