Motorola DSP56301 User Manual

Page 183

Host-Side Programming Model

Host Interface (HI32)

6

-65

read/write command is in progress and the PCI address is $04. In Self-Configuration mode

(DCTR[DCTR[HM]] = $5), the DSP56300 core can indirectly access the CCMR (see Section

6.5.5, Self-Configuration Mode (DCTR[HM] = $5), on page 6-16). The host writes to

CSTR/CCMR in accordance with the byte enables. Byte lanes that are not enabled are not

written, and the corresponding bits remain unchanged. The host can access CSTR/CCMR

only in PCI mode (DCTR[HM]

≠

$1).

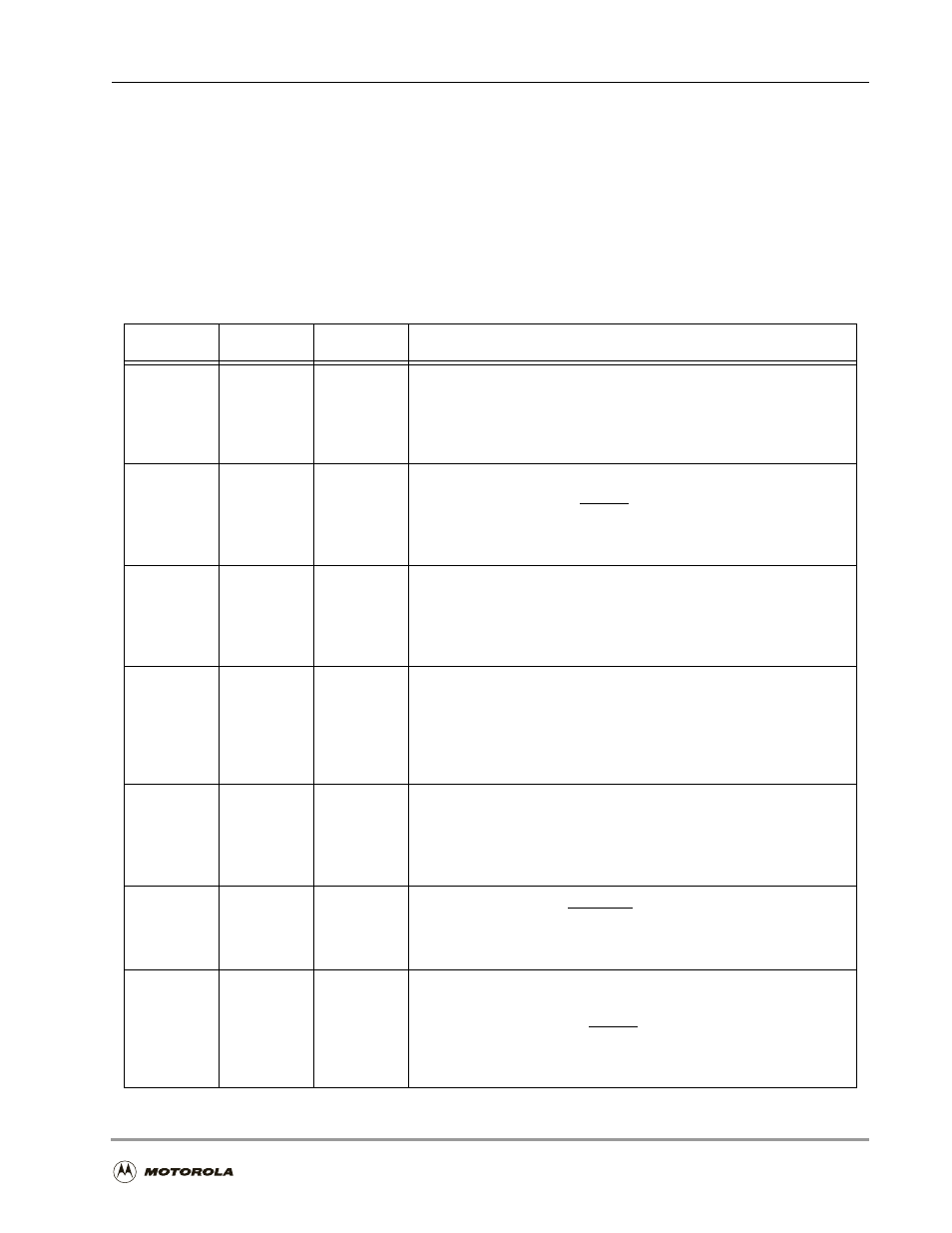

Table 6-26. Status/Command Configuration Register (CSTR/CCMR) Bit Definitions

Bit Number

Bit Name

Reset Value

Description

31

DPE

0

Detected Parity Error

Indicates that the HI32 hardware has detected a parity error. In PCI

mode (DCTR[HM]

=

$1), DPE is set when the HI32 detects either an

address or data parity error. DPE is cleared when the host processor

writes a value of one to it. The personal hardware reset clears DPE.

30

SSE

0

Signaled System Error

Indicates a system error. In PCI mode (DCTR[HM]

=

$1), SSE is set

when the HI32 asserts the HSERR pin. SSE is cleared when the host

processor writes a value of one to it. The personal hardware reset

clears SSE.

29

RMA

0

Received Master Abort

Indicates a master-abort PCI bus state. In PCI mode (HM

=

$1), RMA is

set when the HI32, as a master device, terminates its transaction with

master-abort. RMA is cleared when the host processor writes a value of

one to it. The personal hardware reset clears RMA.

28

RTA

0

Received Target Abort

Indicates a target-abort PCI bus event. In PCI mode (DCTR[HM]

=

$1),

RTA is set when the HI32, as a master device, detects that its

transaction is terminated with target-abort. RTA is cleared when the

host processor writes a value of one to it. The personal hardware reset

clears RTA.

27

STA

0

Signalled Target Abort

Indicates a target-abort PCI bus event. In PCI mode (DCTR[HM]

=

$1),

STA is set when the HI32, as a target device, terminates a transaction

with target-abort. STA is cleared when the host processor writes a value

of one to it. The personal hardware reset clears STA.

26–25

DST[1–0]

0

DEVSEL Timing (hardwired to $1)

Encode the timing of the HDEVSEL pin in PCI mode (DCTR[HM]

=

$1).

DST[1–0] are hardwired to DST = $1, indicating that the HI32 belongs

to the medium DEVSEL timing class of the PCI devices.

24

DPR

0

Data Parity Reported

Indicates the detection of a data parity error in PCI mode (DCTR[HM]

=

$1). The DPR is set when the HI32 acts as a bus master and detects a

data parity error or samples HPERR asserted while CCMR[PERR] is

set. DPR is cleared when the host processor writes a value of one to it.

The personal hardware reset clears DPR.