1 triple timer modes, 1 timer gpio (mode 0), Triple timer modes -6 – Motorola DSP56301 User Manual

Page 268: Timer gpio (mode 0) -6, 1 triple timer modes

Operating Modes

9

-6

DSP56301 User’s Manual

9.3.1

Triple Timer Modes

For all triple timer modes, the following points are true:

n

The TCSR[TE] bit is set to clear the counter and enable the timer. Clearing TCSR[TE]

disables the timer.

n

The value to which the timer is to count is loaded into the TCPR. (This is true for all

modes except the measurement modes (modes 4 through 6).

n

The counter is loaded with the TLR value on the first clock.

n

If the counter overflows, TCSR[TOF] is set, and if TCSR[TOIE] is set, an overflow

interrupt is generated.

n

You can read the counter contents at any time from the Timer Count Register (TCR).

9.3.1.1 Timer GPIO (Mode 0)

In Mode 0, the timer generates an internal interrupt when a counter value is reached, if the

timer compare interrupt is enabled (see Figure 9-3 and Figure 9-4). When the counter equals

the TCPR value, TCSR[TCF] is set and a compare interrupt is generated if the TCSR[TCIE]

bit is set. If the TCSR[TRM] bit is set, the counter is reloaded with the TLR value at the next

timer clock and the count is resumed. If TCSR[TRM] is cleared, the counter continues to

increment on each timer clock signal. This process repeats until the timer is disabled.

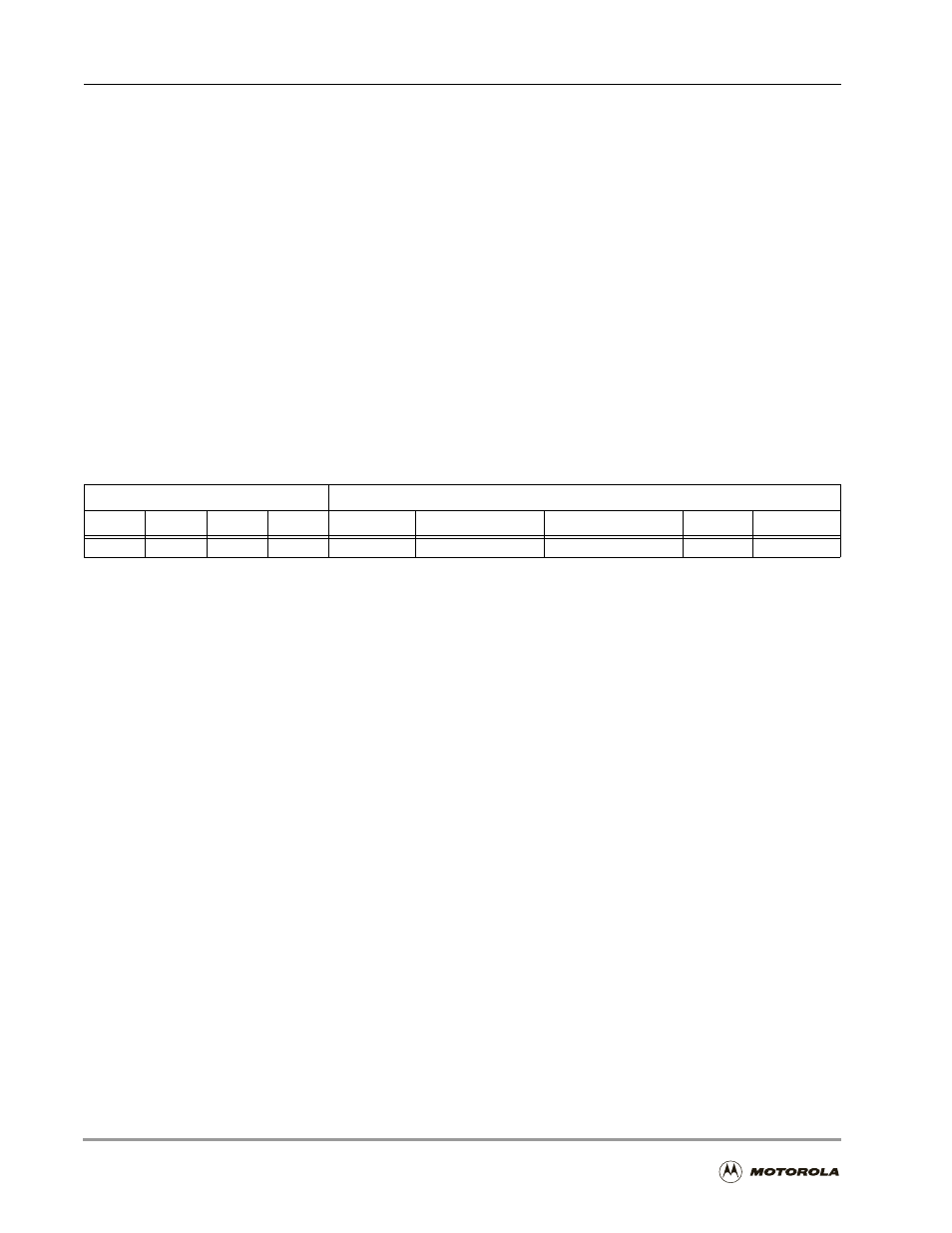

Bit Settings

Mode Characteristics

TC3

TC2

TC1

TC0

Mode

Name

Function

TIO

Clock

0

0

0

0

0

GPIO

Timer

GPIO

Internal