Motorola DSP56301 User Manual

Page 155

HI32 DSP-Side Programming Model

Host Interface (HI32)

6

-37

1

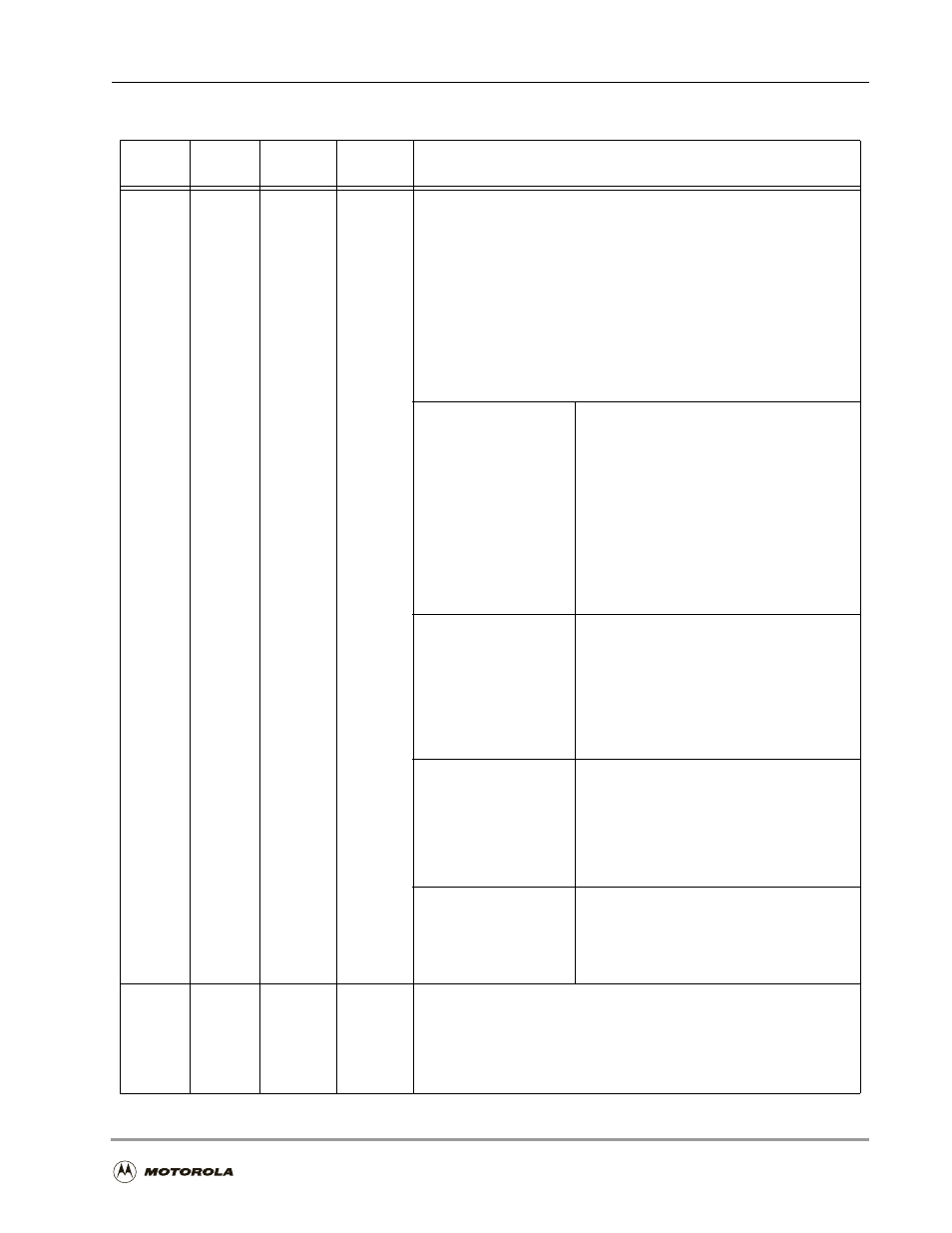

STRQ

1

UBM

PCI

Slave Transmit Data Request

Indicates that the slave transmit data FIFO (DTXS) is not full and the

DSP56300 core can write to it. STRQ functions in accordance with the

value of the slave fetch type (SFT) bit in the Host Control Register

(HCTR). In Fetch mode, the HI32 requests data from the DSP56300

core (by enabling the STRQ status bit and generating core interrupt

requests or DMA requests, if enabled), only after the host begins a read

transaction from the HI32. In Pre-Fetch mode when the DTXS is not full,

the HI32 requests data from the DSP56300 core (by enabling the STRQ

status bit and generating core interrupt requests or DMA requests if

enabled). Hardware, software, and personal software resets set STRQ.

In the personal software reset state, STRQ = 0.

PCI mode (DCTR[HM] =

$1)

Fetch (SFT = 1): The DSP-to-host data path

is a six word deep FIFO buffer (three word

deep in the 32-bit data format mode,

HCTR[HRF] = $0). During a read transaction

from the DTXS-HRXS FIFO, STRQ reflects

the status of the DTXS. STRQ is set if the

DTXS is not full. STRQ is cleared when the

DSP56300 core fills the DTXS. When the

host is not executing a read transaction from

the HRXS, the DSP-to-host data path is

forced to the reset state and STRQ is

cleared.

Universal Bus mode

(DCTR[HM] = $2 or $3)

Fetch (SFT = 1): There is no FIFO buffering

of the DSP-to-host data path. At the

beginning of a read data transfer from the

HRXS, STRQ is set. STRQ is cleared when

the DSP56300 core writes to the DTXS. If the

host is not reading from the HRXS, the

DSP-to-host data path is forced to the reset

and STRQ is cleared.

PCI and Universal Bus

modes (DCTR[HM] = $1,

$2 or $3)

Pre-Fetch (SFT = 0): The DSP-to-host data

path is a six word deep FIFO buffer (three

word deep in the 32-bit data format mode,

DCTR[HM] = $1 and HCTR[HRF] = $0).

STRQ is set if the DTXS is not full. STRQ is

cleared when the DSP56300 core fills the

DTXS.

STRQ is set

n

When STIE is set, a slave transmit

data interrupt request is generated.

n

When enabled by a DSP56300 core

DMA channel, a slave transmit data

DMA request is generated.

0

HCP

0

UBM

PCI

Host Command Pending

Indicates that the host has set the HC bit and that a host command

interrupt is pending. The HCP bit reflects the status of the HC bit in the

HCVR. If HCP is set and HCIE is set, a host command interrupt request

is generated. The HI32 interrupt logic hardware clears HC and HCP

when the HC interrupt request is serviced. The host cannot clear HC.

Table 6-14. DSP Status Register (DSR) Bit Definitions (Continued)

Bit

Number

Bit Name

Reset

Value

Mode

Description