Motorola DSP56301 User Manual

Page 152

HI32 DSP-Side Programming Model

6

-34

DSP56301 User’s Manual

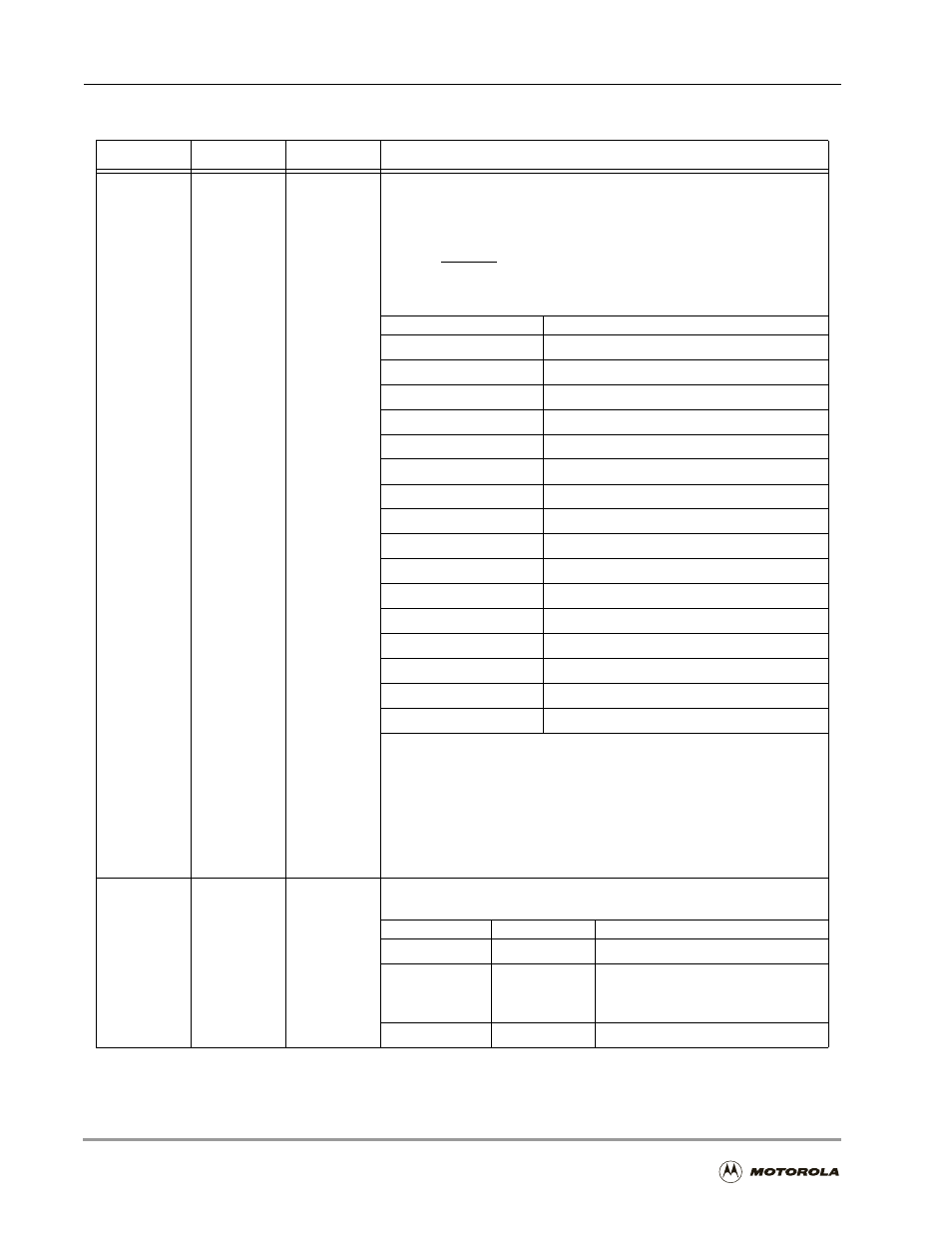

19–16

C[3–0]

0

PCI Bus Command

Defines the PCI bus command. When the DSP56300 core writes to the

DPAR and the HI32 is in PCI mode (DCTR[HM] = $1), ownership of the

PCI bus is requested. When the request is granted, the address is

driven to the HAD[31–0] pins and the bus command is driven to the

HC[3–0]/HBE[3–0] pins during the PCI address phase. PCI bus

commands that the HI32 supports as a PCI master are listed here. The

HI32 does not support illegal values, and they should not be used.

C[3–0]

Command Type

0000

Illegal

0001

Illegal

0010

I/O Read

0011

I/O Write

0100

Illegal

0101

Illegal

0110

Memory Read

0111

Memory Write

1000

Illegal

1001

Illegal

1010

Configuration Read

1011

Configuration Write

1100

Memory Read Multiple

1101

Illegal

1110

Memory Read Line

1111

Memory Write and Invalidate

Note:

When the Memory Write and Invalidate command is used, a

minimum transfer of one complete cache line should be

guaranteed, reflected by the Burst Length value used (BL[5–

0] in the DMPC). The cache line size is set by the PCI

configurator in the Cache Line Size Configuration Register

(CCLS). The DSP56300 core cannot access this value, so the

system must provide the CCLS value to the DSP56300 core in

another user-defined way.

15–0

AR[15–0]

0

DSP PCI Transaction Address (Low)

In memory accesses, the AR[1–0] bits have the following meaning:

AR1

AR0

Burst Order

0

0

Linear incrementing

0

1

PCI Cache line toggle mode (the

data must be arranged by the DSP

software)

1

X

Reserved

Table 6-13. DSP PCI Address Register (DPAR) Bit Definitions (Continued)

Bit Number

Bit Name

Reset Value

Description