9 hi32 programming model/quick reference, Hi32 programming model/quick reference -74, 9 hi32 programming model/quick reference – Motorola DSP56301 User Manual

Page 192

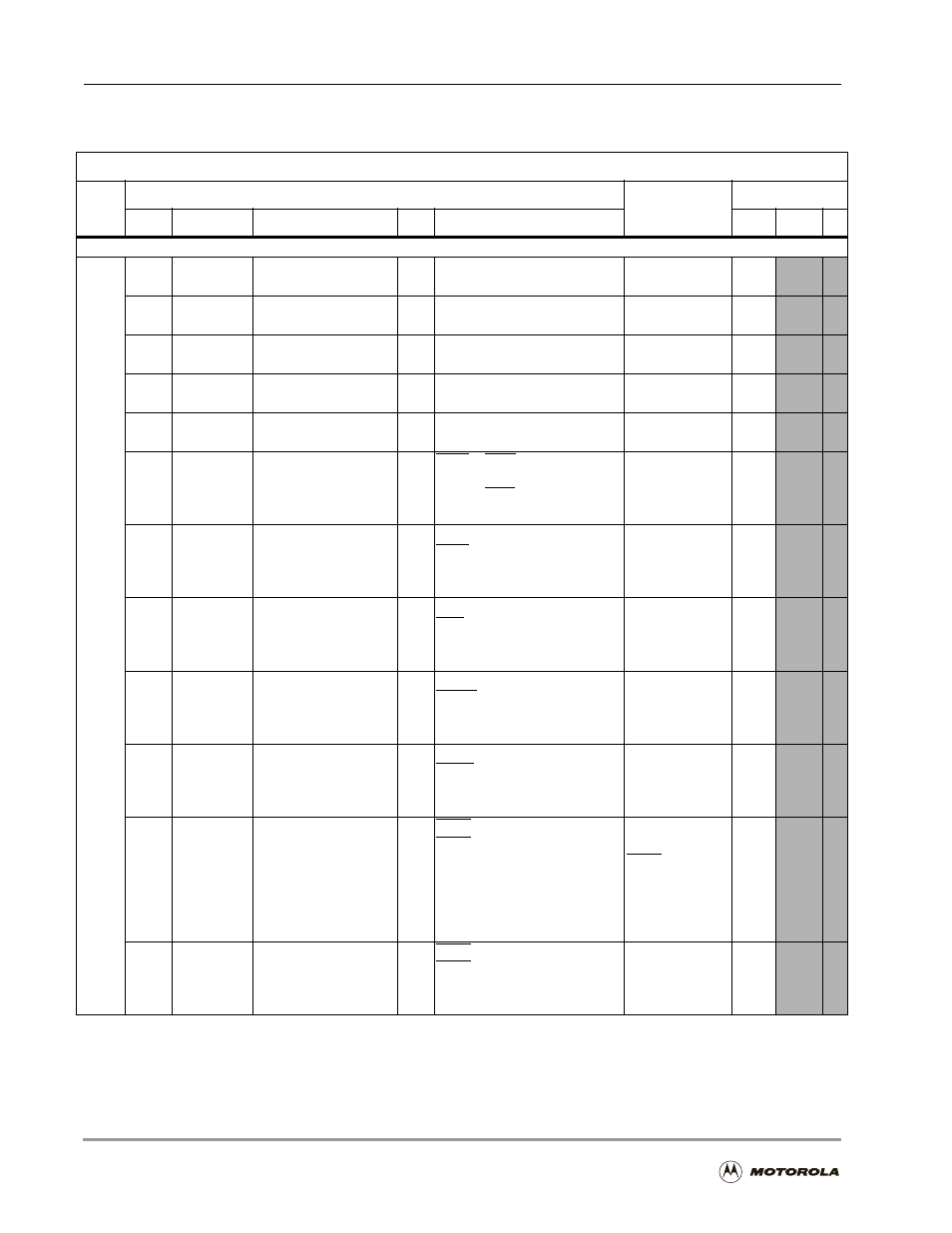

HI32 Programming Model/Quick Reference

6

-74

DSP56301 User’s Manual

6.9

HI32 Programming Model/Quick Reference

HI32 Registers—Quick Reference

Reg

Bit

Comments

Reset Type

Num

Mnemonic

Name

Val

Function

HS

PH

PS

DSP SIDE

DCTR

0

HCIE

Host Command

Interrupt Enable

0

1

HCP interrupt disabled

HCP interrupt enabled

0

-

-

1

STIE

Slave Transmit

Interrupt Enable

0

1

STRQ interrupt disabled

STRQ interrupt enabled

0

-

-

2

SRIE

Slave Receive

Interrupt Enable

0

1

SRRQ interrupt disabled

SRRQ interrupt enabled

0

-

-

5-3

HF[5–3]

Host Flags

general-purpose

flags

$0

-

-

6

HINT

Host Interrupt A

0

1

HINTA pin is high impedance

HINTA pin is driven low

0

13

HDSM

Host Data Strobe

Mode

0

1

HWR + HRD (double data

strobe)

HRW + HDS (single data

strobe)

changed only in

PS reset;

ignored when

not in UBM

0

-

-

14

HRWP

Host RD/WR Polarity

0

1

HRW (0 = WRITE, 1 = READ)

HRW(0 = READ, 1 = WRITE)

changed only in

PS reset;

ignored when

not in UBM

0

-

-

15

HTAP

Host Transfer

Acknowledge Polarity

0

1

HTA

HTA

changed only in

PS reset;ignored

when not in

UBM

0

-

-

16

HDRP

Host DMA Request

Polarity

0

1

HDRQ

HDRQ

changed only in

PS reset;ignored

when not in

UBM

0

-

-

17

HRSP

Host Reset Polarity

0

1

HRST

HRST

changed only in

PS reset;ignored

when not in

UBM

0

-

-

18

HIRH

Host Interrupt Request

Handshake Mode

0

1

HIRQ pulsed

HIRQ = full handshake

changed only in

PS reset

HIRQ pulse

width is defined

by CLAT;

ignored when

not in UBM

0

-

-

19

HIRD

Host Interrupt Request

Drive Control

0

1

HIRQ = open drain

HIRQ = driven

changed only in

PS reset;

ignored when

not in UBM

0

-

-