Motorola DSP56301 User Manual

Page 97

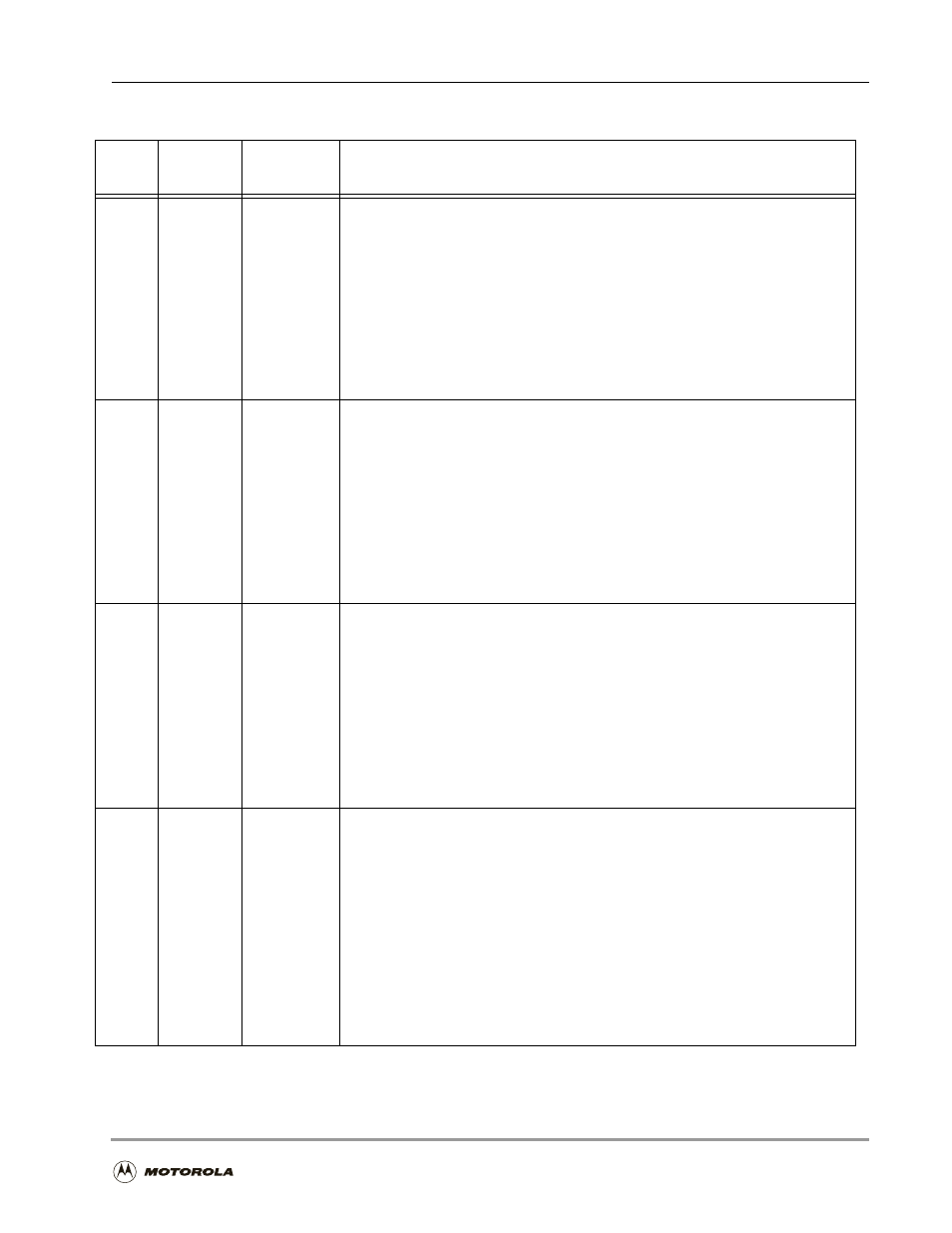

Bus Interface Unit (BIU) Registers

Core Configuration

4

-23

20–16

BDFW[4–0]

11111

(31 wait

states)

Bus Default Area Wait State Control

Defines the number of wait states (one through 31) inserted into each external

access to an area that is not defined by any of the AAR registers. The access type

for this area is SRAM only. These bits should not be programmed as zero since

SRAM memory access requires at least one wait state.

When four through seven wait states are selected, one additional wait state is

inserted at the end of the access. When selecting eight or more wait states, two

additional wait states are inserted at the end of the access. These trailing wait

states increase the data hold time and the memory release time and do not

increase the memory access time.

15–13

BA3W[2–0]

111

(7 wait states)

Bus Area 3 Wait State Control

Defines the number of wait states (one through seven) inserted in each external

SRAM access to Area 3 (DRAM accesses are not affected by these bits). Area 3 is

the area defined by AAR3.

Note:

Do not program the value of these bits as zero since SRAM memory

access requires at least one wait state.

When four through seven wait states are selected, one additional wait state is

inserted at the end of the access. This trailing wait state increases the data hold

time and the memory release time and does not increase the memory access time.

12–10

BA2W[2–0]

111

(7 wait states)

Bus Area 2 Wait State Control

Defines the number of wait states (one through seven) inserted into each external

SRAM access to Area 2 (DRAM accesses are not affected by these bits). Area 2 is

the area defined by AAR2.

Note:

Do not program the value of these bits as zero, since SRAM memory

access requires at least one wait state.

When four through seven wait states are selected, one additional wait state is

inserted at the end of the access. This trailing wait state increases the data hold

time and the memory release time and does not increase the memory access time.

9–5

BA1W[4–0]

11111

(31 wait

states)

Bus Area 1 Wait State Control

Defines the number of wait states (one through 31) inserted into each external

SRAM access to Area 1 (DRAM accesses are not affected by these bits). Area 1 is

the area defined by AAR1.

Note:

Do not program the value of these bits as zero, since SRAM memory

access requires at least one wait state.

When four through seven wait states are selected, one additional wait state is

inserted at the end of the access. When selecting eight or more wait states, two

additional wait states are inserted at the end of the access. These trailing wait

states increase the data hold time and the memory release time and do not

increase the memory access time.

Table 4-9. Bus Control Register (BCR) Bit Definitions (Continued)

Bit

Number

Bit Name

Reset Value

Description