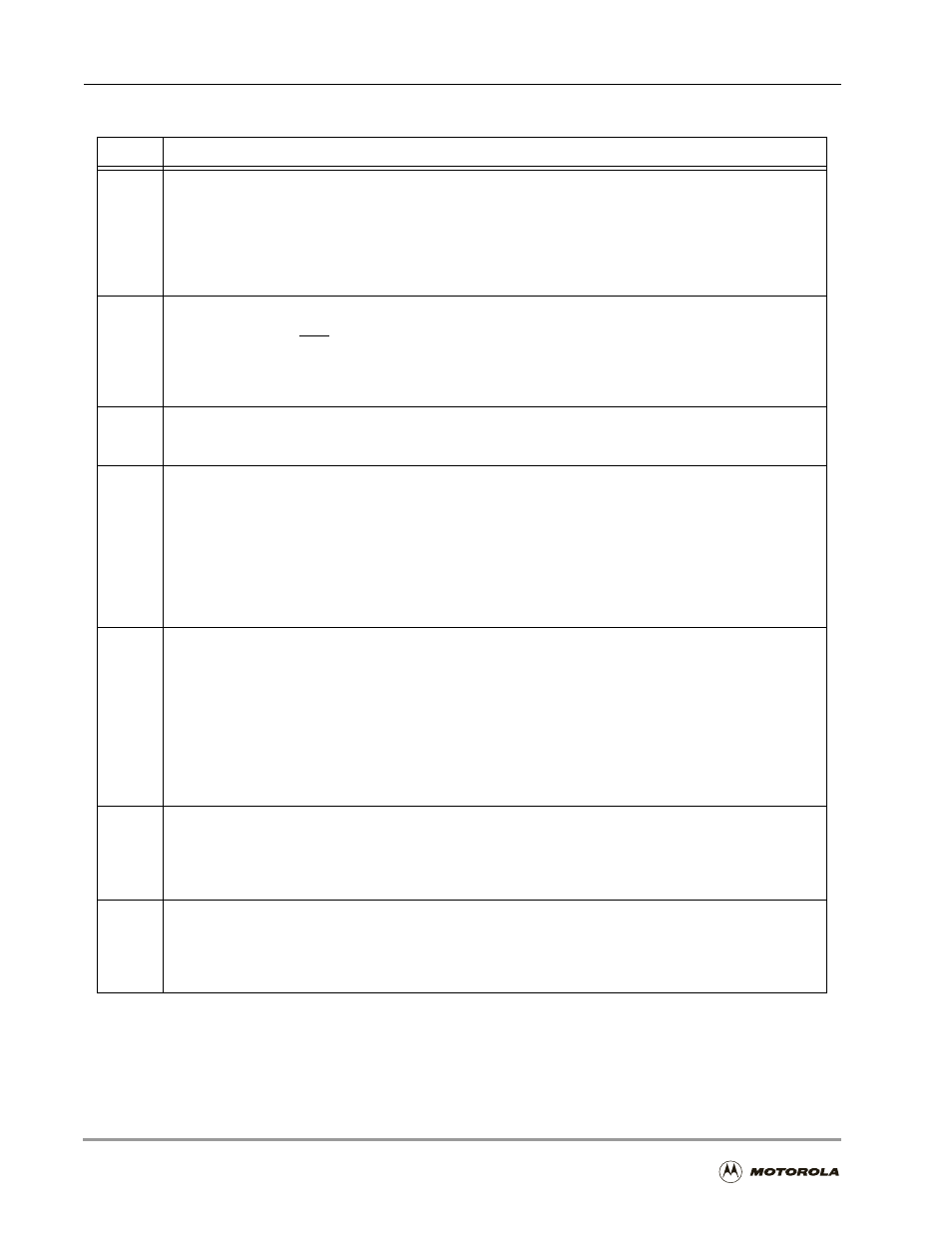

Table 4-2. operating mode definitions (continued) – Motorola DSP56301 User Manual

Page 78

Operating Modes

4

-4

DSP56301 User’s Manual

6

Host bootstrap 8-bit wide UB mode in double-strobe pin configuration—The hardware reset vector

is located at address $FF0000 in the bootstrap ROM. The program bootstraps through HI32 in UB slave

double-strobe (HWR, HRD) configuration. The DSP56301 is written with 24-bit wide words broken into

8-bit wide host bus transfers. You can use this mode for booting from various microprocessors or

microcontrollers—for example, booting a slave DSP56301 from port A of a master DSP563xx.

Note:

DSP CLKOUT rate must be at least three times the data transfer rate.

7

Host bootstrap 8-bit wide UB mode in single-strobe pin configuration—The hardware reset vector is

at address $FF0000 in the bootstrap ROM. The program bootstraps through HI32 in UB slave

single-strobe (HRW, HDS) configuration. The DSP56301 is written with 24-bit wide words using 8-bit wide

host bus transfers. You can use this mode for booting from various microprocessors or microcontrollers.

Note:

DSP CLKOUT rate must be at least three times the data transfer rate.

8

Expanded mode—Bypasses the bootstrap ROM. The DSP56301 begins fetching instructions, starting at

$008000. Memory accesses are performed using SRAM memory access type with 31 wait states and no

address attributes selected (default).

9

Bootstrap from byte-wide memory—Loads a program memory segment from consecutive byte-wide P

memory locations, starting at P:$D00000 (bits 7-0). The memory is selected by the Address Attribute AA1

and is accessed with 31 wait states. The EPROM bootstrap code expects first to read 3 bytes specifying

the number of program words, then 3 bytes specifying the address to start loading the program words,

and then 3 bytes for each program word to be loaded. The number of words, the starting address, and the

program words are read least significant byte first followed by the middle and then the most significant

byte. The program concatenates consecutive three byte sequences into 24-bit words and stores them in

contiguous PRAM memory locations starting at the specified address. After the program words are read,

program execution starts from the same address where loading started.

A

Bootstrap through SCI—The hardware reset vector is located at address $FF0000 in the bootstrap

ROM. The program bootstraps through the SCI. The bootstrap program sets the SCI to operate in 10-bit

asynchronous mode, with 1 start bit, 8 data bits, 1 stop bit, and no parity. Data is received in this order:

start bit, 8 data bits (LSB first), and one stop bit. Data is aligned in the SCI receive data register with the

LSB of the least significant byte of the received data appearing at Bit 0.The user must provide an external

clock source with a frequency at least 16 times the transmission data rate. Each byte received by the SCI

is echoed back through the SCI transmitter to the external transmitter. The boot program concatenates

every three bytes read from the SCI into a 24-bit wide DSP56301 word.

Note:

DSP CLKOUT rate must be at least 64 times the data transmission rate.

B

Host bootstrap in DSP-to-DSP mode—The hardware reset vector is located at address $FF0000 in the

bootstrap ROM. The program bootstraps through the HI32 in UB mode, double strobe, HTA pin active

low. The DSP56301 is written with 24-bit-wide words.

Note:

DSP CLKOUT rate must be at least three times the data transfer rate.

C

Host bootstrap PCI mode (32-bit wide)—The hardware reset vector is located at address $FF0000 in

the bootstrap ROM. The program bootstraps through the HI32 in standard PCI slave configuration. The

DSP56301 is written with 24-bit-wide words encapsulated in 32-bit wide PCI transfers.

Note:

DSP CLKOUT rate must be 5/3 of the PCI clock.

Table 4-2. Operating Mode Definitions (Continued)

Mode

Description