Motorola DSP56301 User Manual

Page 218

ESSI Programming Model

7

-20

DSP56301 User’s Manual

18

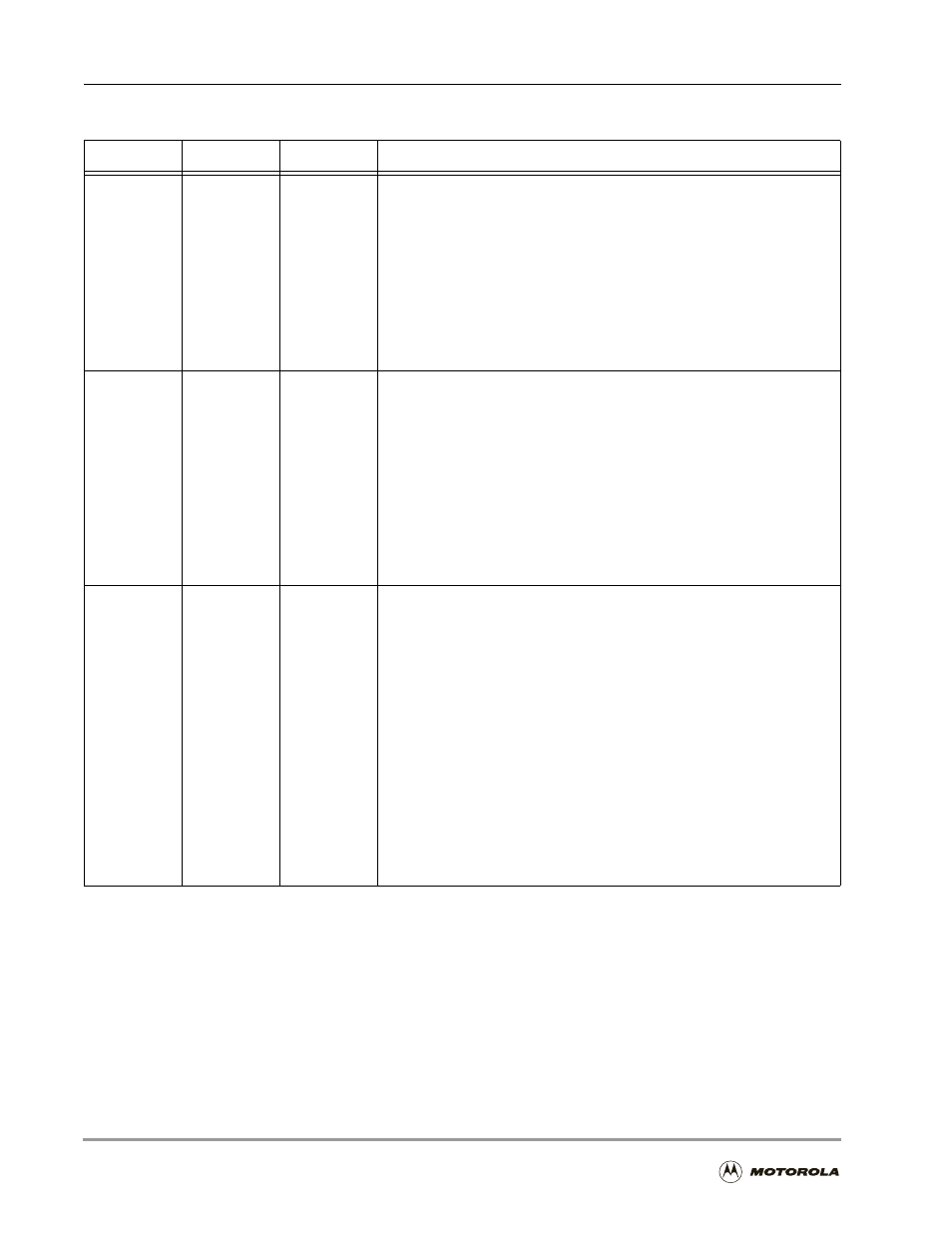

TIE

0

Transmit Interrupt Enable

Enables/disables a DSP transmit interrupt; the interrupt is generated when

both the TIE and the TDE bits in the ESSI status register are set. When

TIE is cleared, the transmit interrupt is disabled. The transmit interrupt is

documented in Section 7.3.3. When data is written to the data registers of

the enabled transmitters or to the TSR, it clears TDE and also clears the

interrupt. Transmit interrupts with exception conditions have higher priority

than normal transmit data interrupts. If the transmitter underrun error

(TUE) bit is set (signaling that an exception has occurred) and the TEIE bit

is set, the ESSI requests an SSI transmit data with exception interrupt

from the interrupt controller.

17

RE

0

Receive Enable

Enables/disables the receive portion of the ESSI. When RE is cleared, the

receiver is disabled: data transfer into RX is inhibited. If data is being

received while this bit is cleared, the remainder of the word is shifted in

and transferred to the ESSI receive data register. RE must be set in both

Normal and On-Demand modes for the ESSI to receive data. In Network

mode, clearing RE and setting it again disables the receiver after

reception of the current data word. The receiver remains disabled until the

beginning of the next data frame.

Note:

The setting of the RE bit does not affect the generation of a

frame sync.

16

TE0

0

Transmit 0 Enable

Enables the transfer of data from TX0 to Transmit Shift Register 0. TE0 is

functional when the ESSI is in either synchronous or Asynchronous mode.

When TE0 is set and a frame sync is detected, the transmitter 0 is enabled

for that frame.

When TE0 is cleared, transmitter 0 is disabled after the transmission of

data currently in the ESSI transmit shift register. The STD output is

tri-stated, and any data present in TX0 is not transmitted. In other words,

data can be written to TX0 with TE0 cleared; the TDE bit is cleared, but

data is not transferred to the transmit shift register 0. The transmit enable

sequence in On-Demand mode can be the same as in Normal mode, or

TE0 can be left enabled.

Note:

Transmitter 0 is the only transmitter that can operate in

Asynchronous mode (SYN = 0). The setting of the TE0 bit does

not affect the generation of frame sync or output flags.

Table 7-4. ESSI Control Register B (CRB) Bit Definitions (Continued)

Bit Number

Bit Name

Reset Value

Description