Motorola DSP56301 User Manual

Page 167

Host-Side Programming Model

Host Interface (HI32)

6

-49

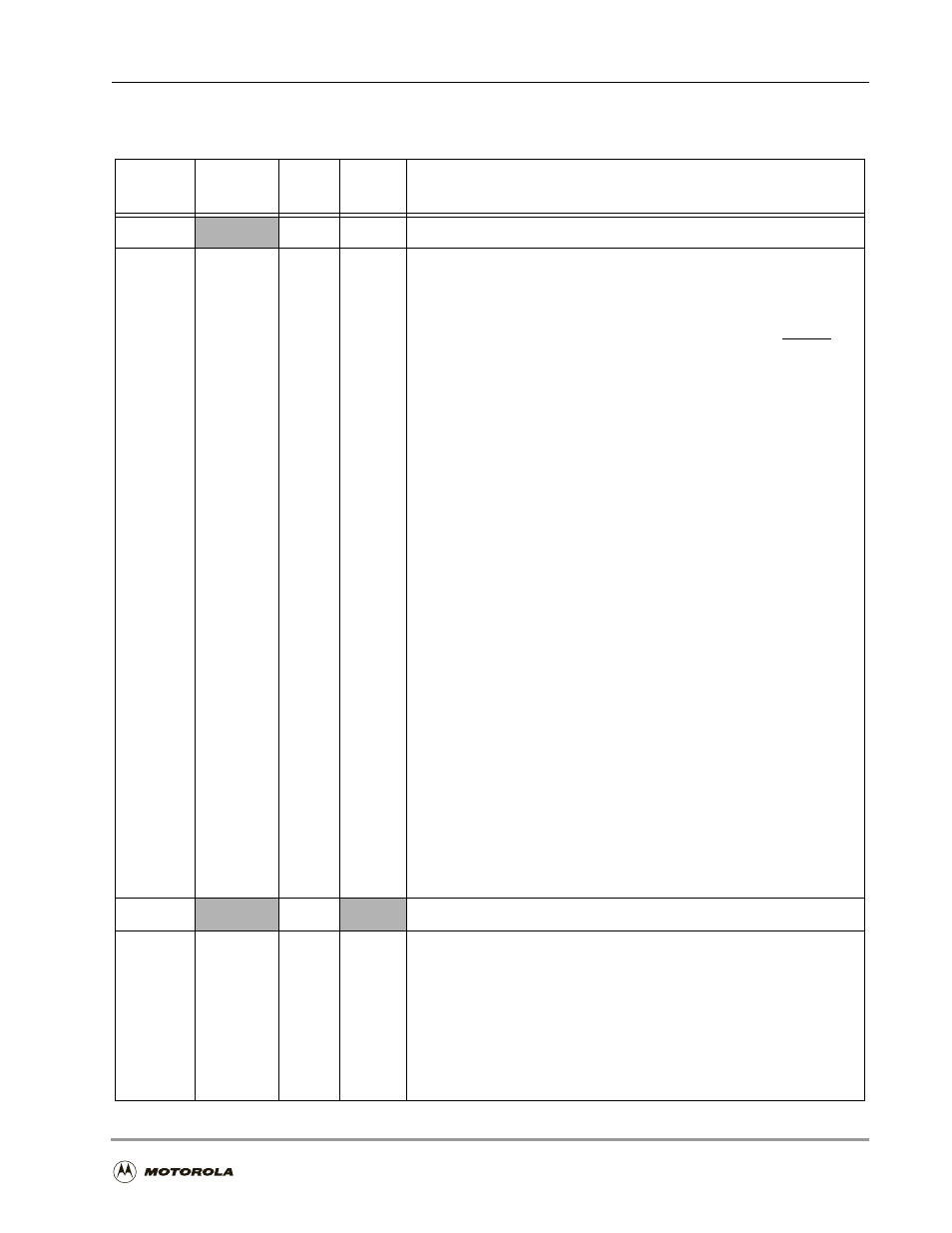

Table 6-22. Host Interface Control Register (HCTR) Bit Definitions

Bit

Number

Bit Name

Reset

Value

Mode

Description

31–20

0

Reserved. Write to zero for future compatibility.

19

TWSD

0

PCI

Target Wait State Disable

Note:

Do not set the TWSD bit. This bit is reserved. The HI32 may

operate improperly in PCI mode when the Target Wait State

Disable (TWSD) bit is set.

Disables PCI wait states (which are inserted by deasserting HTRDY)

during a data phase. If TWSD is cleared and the HI32 is in PCI mode

(DCTR[HM]

=

$1):

n

as the selected target in a read data phase from the HRXS, the

HI32 inserts PCI wait states if the HRXS is empty (HRRQ = 0).

Wait states are inserted until the data is transferred from the DSP

side to the HRXS. Up to eight wait states can be inserted before a

target initiated transaction termination (disconnect-C/Retry) is

generated.

n

as the selected target in a write data phase to the HTXR, the HI32

inserts PCI wait states if the HTXR is full (HTRQ = 0). Wait states

are inserted until the data is transferred from the HTXR to the DSP

side. Up to eight wait states can be inserted before a target

initiated transaction termination (disconnect-C/Retry) is generated.

n

as the selected target in a write data phase to the HCVR, the HI32

inserts PCI wait states if a host command is pending (HC = 1).

Wait states are inserted until the pending host command is

serviced. Up to eight wait states can be inserted before a target

initiated transaction termination (disconnect-C/Retry) is generated.

If TWSD is set and the HI32 is in the PCI mode (DCTR[HM]

=

$1):

n

as the selected target in a read transaction from the HRXS, the

HI32 generates a target initiated transaction termination

(disconnect-C) if the HRXS is empty (HRRQ = 0).

n

as the selected target in a write transaction to the HTXR, the HI32

generates a target initiated transaction termination (disconnect-C)

if the HTXR is full (HTXR = 0).

n

as the selected target in a write transaction to the HCVR, the HI32

generates a target initiated transaction termination (disconnect-C)

if a host command is pending (HC = 1).

TWSD is ignored when the HI32 is not in PCI mode (DCTR[HM]

≠

$1).

The personal hardware reset clears TWSD.

18–17

0

Reserved. Write to zero for future compatibility.

16–14

HS[2–0] 0

UBM

PCI

Host Semaphores

Used by the host processors for software arbitration of mastership over

the HI32. These bits do not affect the HI32 operation and serve only as a

read/write semaphore repository. These bits can be used as a mailbox

between the external hosts. For example, the semaphores can assist

HI32 bus arbitration among several external hosts. All external host

processors that compete for mastership over the HI32 should work

according to the same software protocol for handling over the HI32 from

one host processor to another.