Figure b-5, Phase-locked loop control register (pctl), Programming sheets – Motorola DSP56301 User Manual

Page 329: B-17, Application: date: programmer

Programming Sheets

Programming Reference

B

-17

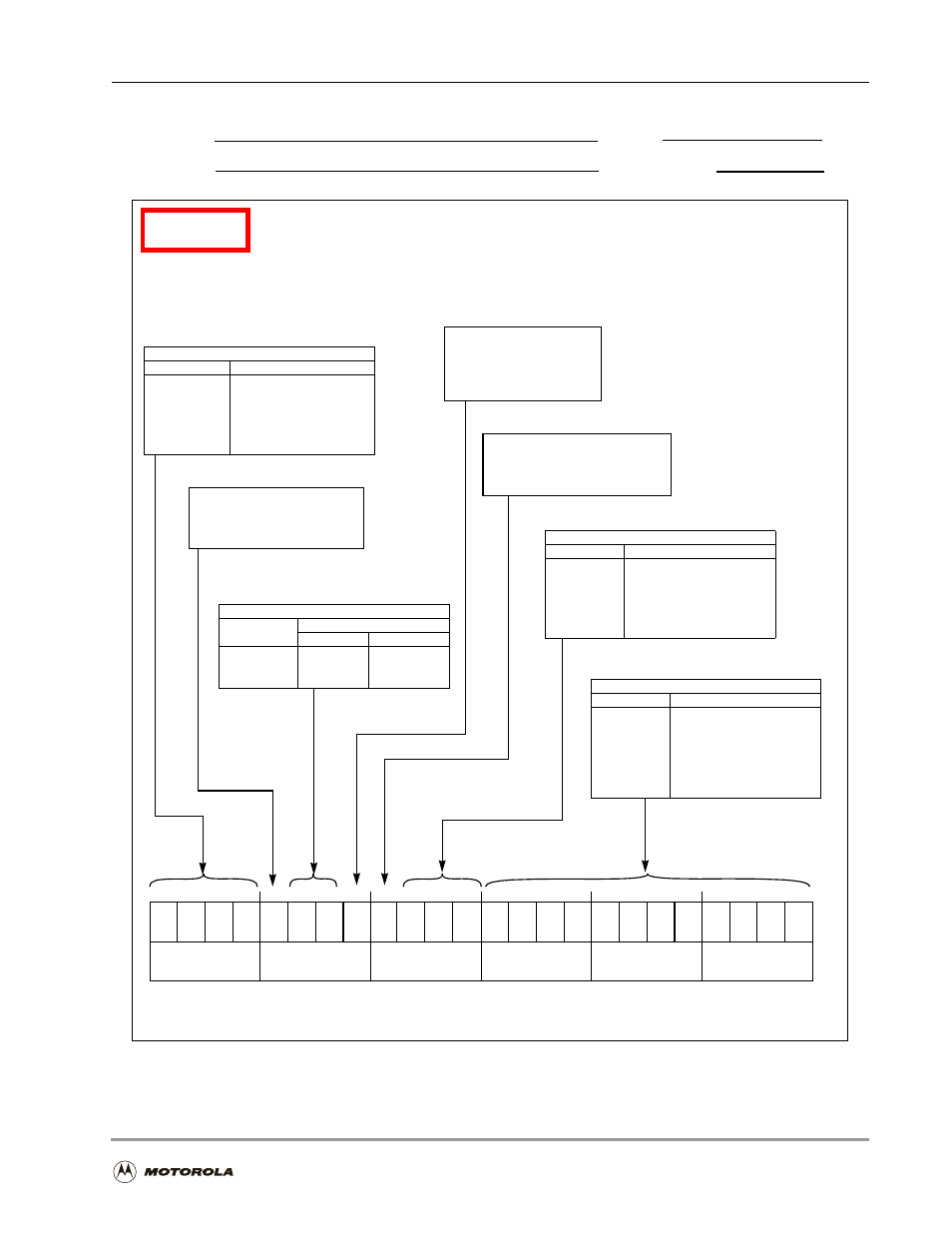

Figure B-5. Phase-Locked Loop Control Register (PCTL)

Application:

Date:

Programmer:

Sheet 1 of 1

PLL

15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

MF7

MF5

MF4

MF3

MF2

MF1 MF0

19 18 17 16

23 22 21 20

PEN

COD

PD1

PD3

MF6

PD2

XTLD XTLR DF2

DF1

DF0 MF11

PD0

PSTP

MF10 MF9

MF8

PLL Control Register (PCTL)

X:$FFFFFD Read/Write

Reset = $000000

XTAL Disable Bit (XTLD)

0 = Enable Xtal Oscillator

1 = EXTAL Driven From

An External Source

Clock Output Disable (COD)

0 = 50% Duty Cycle Clock

1 = Pin Held In High State

Crystal Range Bit (XTLR)

0 = External Xtal Freq > 200KHz

1 = External Xtal Freq < 200KHz

Predivision Factor Bits (PD0–PD3)

PD3–PD0

Predivision Factor PDF

$0

$1

$2

•

•

•

$F

1

2

3

•

•

•

16

Multiplication Factor Bits MF0–MF11

MF11–MF0

Multiplication Factor MF

$000

$001

$002

•

•

•

$FFF

$FFF

1

2

3

•

•

•

4095

4096

PSTP and PEN Relationship

PSTP

PEN

Operation During STOP

PLL

Oscillator

0

1

Disabled

Disabled

1

0

Disabled

Enabled

1

1

Enabled

Enabled

Division Factor Bits (DF0–DF2)

DF2–DF0

Division Factor DF

$0

$1

$2

•

•

•

$7

2

0

2

1

2

2

•

•

•

2

7