Motorola DSP56301 User Manual

Page 145

HI32 DSP-Side Programming Model

Host Interface (HI32)

6

-27

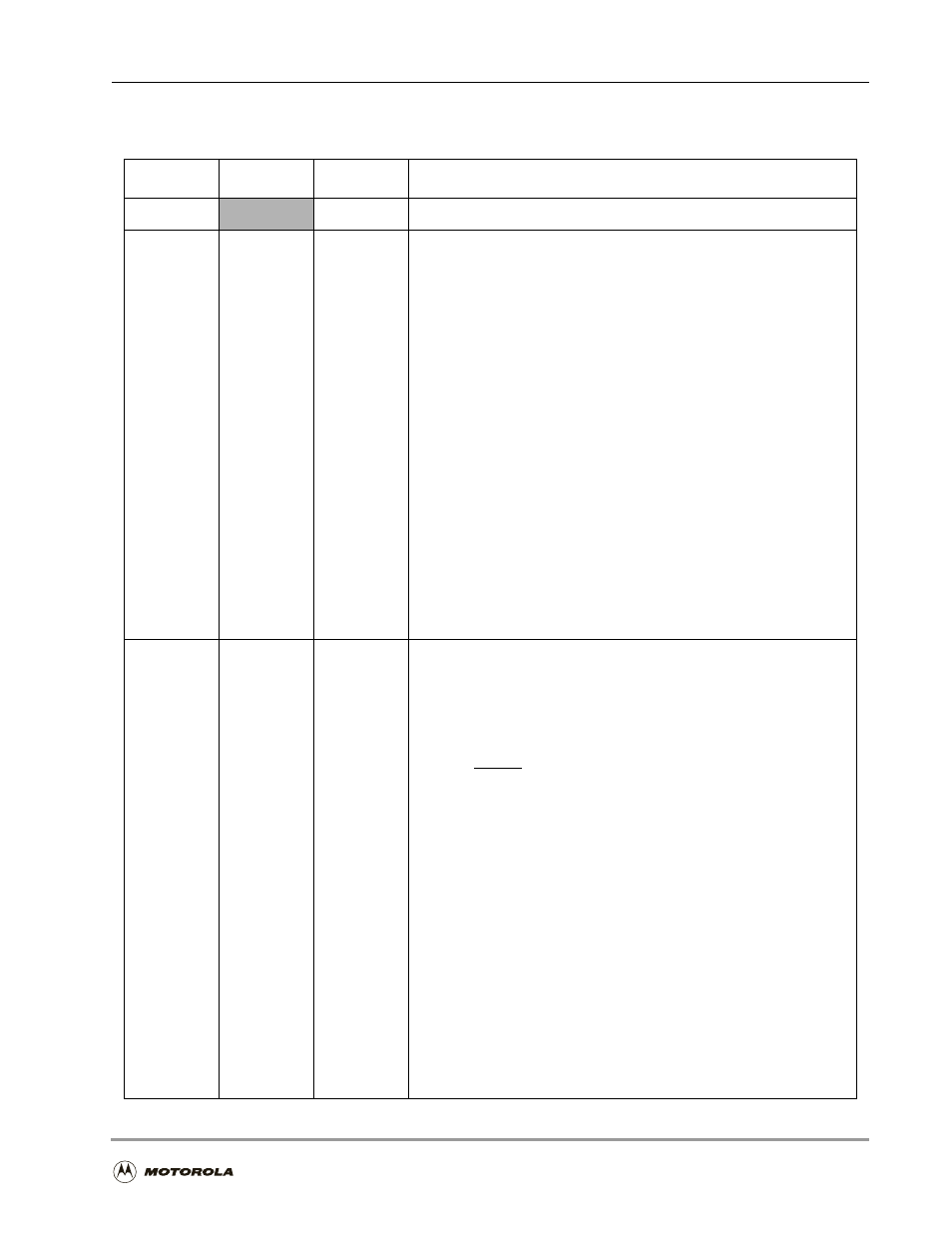

Table 6-11. DSP PCI Control Register (DPCR) Bit Definitions

Bit Number

Bit Name

Reset Value

Description

23–22

0

Reserved. Write to 0 for future compatibility.

21

IAE

0

Insert Address Enable

In PCI mode (DCTR[HM] = $1), inserts the PCI transaction address at

the head of the incoming data stream in accordance with the value of

the host data transfer format (HTF) bits in the HCTR. When IAE is set,

the HI32 writes the PCI transaction address to the HTXR before the

data written by the host, if the HI32 is accessed in a write transaction.

In 32-bit mode, the two least significant bytes of the PCI transaction

address are written to the two least significant bytes of the HTXR. Then

the two most significant bytes of the PCI transaction address are

inserted as 00HHHH, $00LLLL, where HHHH = HAD[31:16] and LLLL

= HAD[15–0]). If HCTR[HTF]

≠

$0, only the two least significant bytes of

the PCI transaction address are written to the two least significant bytes

of the HTXR (the address is inserted as $00LLLL, where LLLL =

HAD[15–0]). The incoming data is written to the HTXR after the

address.

IAE is ignored when the HI32 is not in the PCI mode (DCTR[HM]

≠

$1).

The value of IAE can change only when DSR[HACT] = 0 or HDTC = 1.

Note:

When the HI32 is in PCI mode, the Insert Address Enable

control bit (IAE = 1) can be set only when the Receive Buffer

Lock Enable control bit is set (RBLE = 1 in the DPCR).

20

RBLE

0

Receive Buffer Lock Enable

In PCI mode (DCTR[HM] = $1), assures that the host-to-DSP data path

contains data from only one external master. RBLE inhibits the HI32

from responding to new PCI write transactions to the HTXR until the

DSP56300 core reads all the data written to the HTXR. When RBLE is

set and one of the following conditions occurs:

n

a non-exclusive write transaction to the HTXR

n

an HLOCK deassertion completes after an exclusive write

access to the HTXR

n

a read transaction initiated by the HI32 completes

then the following situations occur:

n

Forthcoming PCI write accesses to the HTXR are disconnected

(retry or disconnect-C) until the DSP56300 core writes a value of

one to the host data transfer complete (HDTC) bit in the DPSR.

n

If the host-to-DSP data path is empty (SRRQ = 0 and MRRQ = 0)

because of DSP56300 core reads from the DRXR, the HDTC bit

is set. The HI32 disconnects (retry or disconnect-C) all PCI write

accesses to the HTXR until the DSP56300 core writes a value of

one to the HDTC bit to clear it.

When RBLE is cleared, the HI32 does not set the HDTC bit. If the

HDTC bit is cleared, the HI32 responds to write PCI transactions

according to the status of the host-to-DSP data path.

RBLE is ignored when the HI32 is not in the PCI mode (DCTR[HM]

≠

$1).

The value of RBLE may be changed only when DSR[HACT] = 0 or

HDTC = 1.