4 host master receive data register (hrxm), 5 host slave receive data register (hrxs), Host master receive data register (hrxm) -61 – Motorola DSP56301 User Manual

Page 179: Host slave receive data register (hrxs) -61, 4 host master receive data register (hrxm), 5 host slave receive data register (hrxs)

Host-Side Programming Model

Host Interface (HI32)

6

-61

6.8.4

Host Master Receive Data Register (HRXM)

The HRXM is the output stage of the master DSP-to-host data path FIFO for DSP-to-host

data transfers. Neither the DSP56300 core nor the host can access the HRXM. The HRXM

transfers the data to the HI32 data pins via the data transfer format converter (HDTFC). The

value of the DPMC[FC] bits define which bytes of the HRXM are output to the pins and their

alignment. (See Section 6.3.2, DSP-To-Host Data Path, on page 6-7 and

Table 6-3, HI32 (PCI Master Data Transfer Formats, on page 6-8).

In PCI mode (DCTR[HM] = $1), the DSP56300 core can clear the HI32 master-to-host bus

data path and empty HRXM by setting the DPCR[CLRT] bit. In PCI DSP-to-host data

transfers via the HRXM, all four byte lanes are driven with data, in accordance with the

FC[1–0] bits, regardless of the value of the byte enable pins (

HC3

/

HBE3

-

HC0

/

HBE0

).

Hardware, software and personal software resets empty the HRXM.

6.8.5

Host Slave Receive Data Register (HRXS)

The HRXS is the output stage of the slave DSP-to-host data path FIFO for DSP-to-host data

transfers. The DSP56300 core cannot access HRXS. The HRXS contains valid data when the

HSTR[HRRQ] bit is set. Emptying the HRXS by host processor reads clears HSTR[HRRQ].

The HRXS transfers the data to the HI32 data pins via the data transfer format converter

(HDTFC). The value of the HCTR[HRF] bits define which bytes of the HRXS are output to

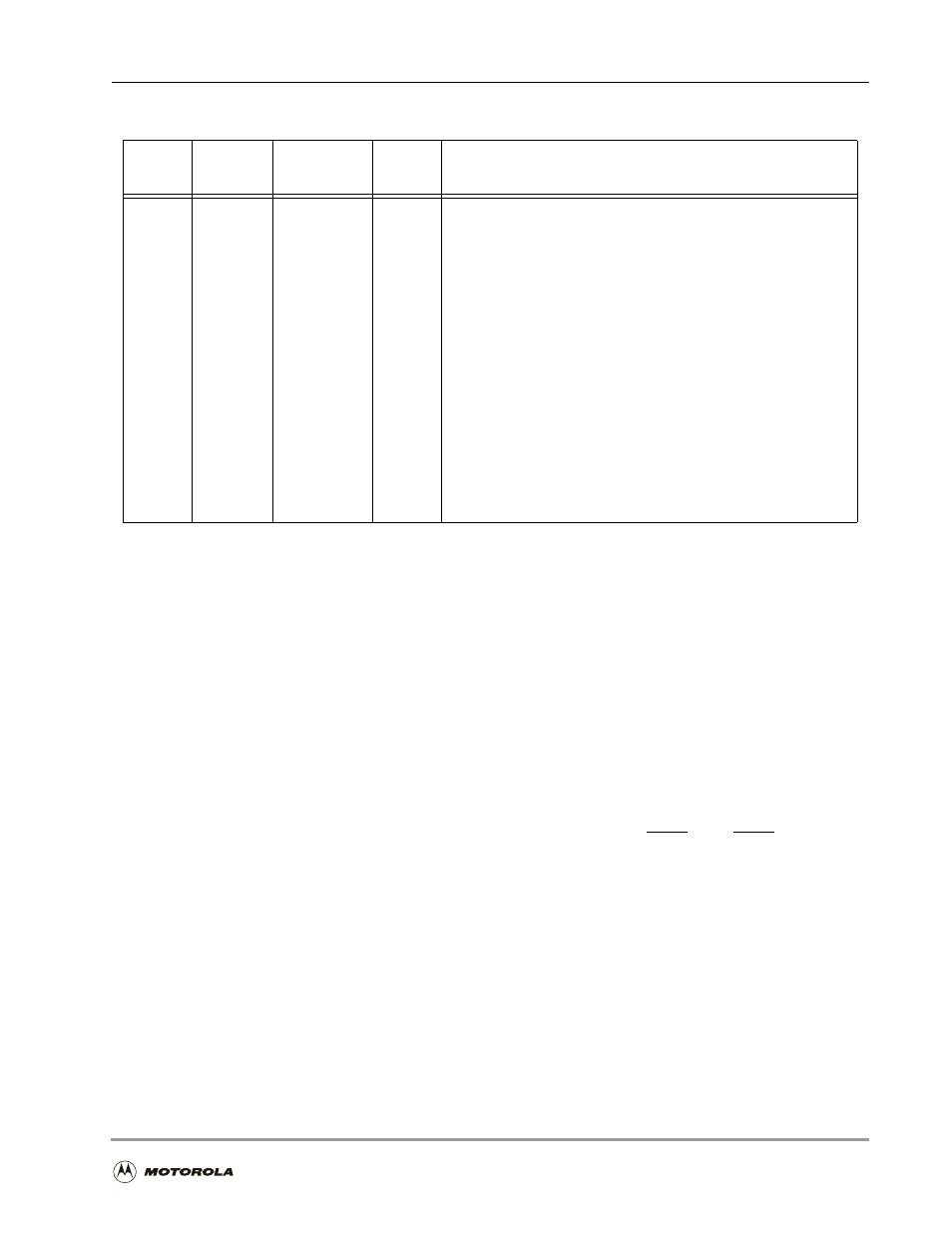

0

HC

0

UBM

PCI

Host Command

Used by the host processor to handshake the execution of host

command interrupt requests. Normally, the host processor sets

HC to request a host command interrupt from the DSP56300 core.

When the DSP56300 core acknowledges the host command

interrupt request, HI32 hardware clears the HC bit. The host

processor can read the state of HC to determine when the host

command request is serviced. The host processor cannot clear

HC. Setting HC causes host command pending (HCP) to be set in

the DSR. The host can write HC and HV in the same write cycle if

desired. If HC is set:

n

In the PCI mode: The HI32 is a target in a write data phase

to the HCVR. It deasserts HTRDY and inserts up to eight

PCI wait cycles until HC is cleared.

n

In a Universal Bus mode: In a write transaction to the

HCVR, the HI32 slave deasserts HTA until HC is cleared.

Table 6-24. Host Command Vector Register (HCVR) Bit Definitions (Continued)

Bit

Number

Bit Name

Reset Value

Mode

Description