Motorola DSP56301 User Manual

Page 184

Host-Side Programming Model

6

-66

DSP56301 User’s Manual

23

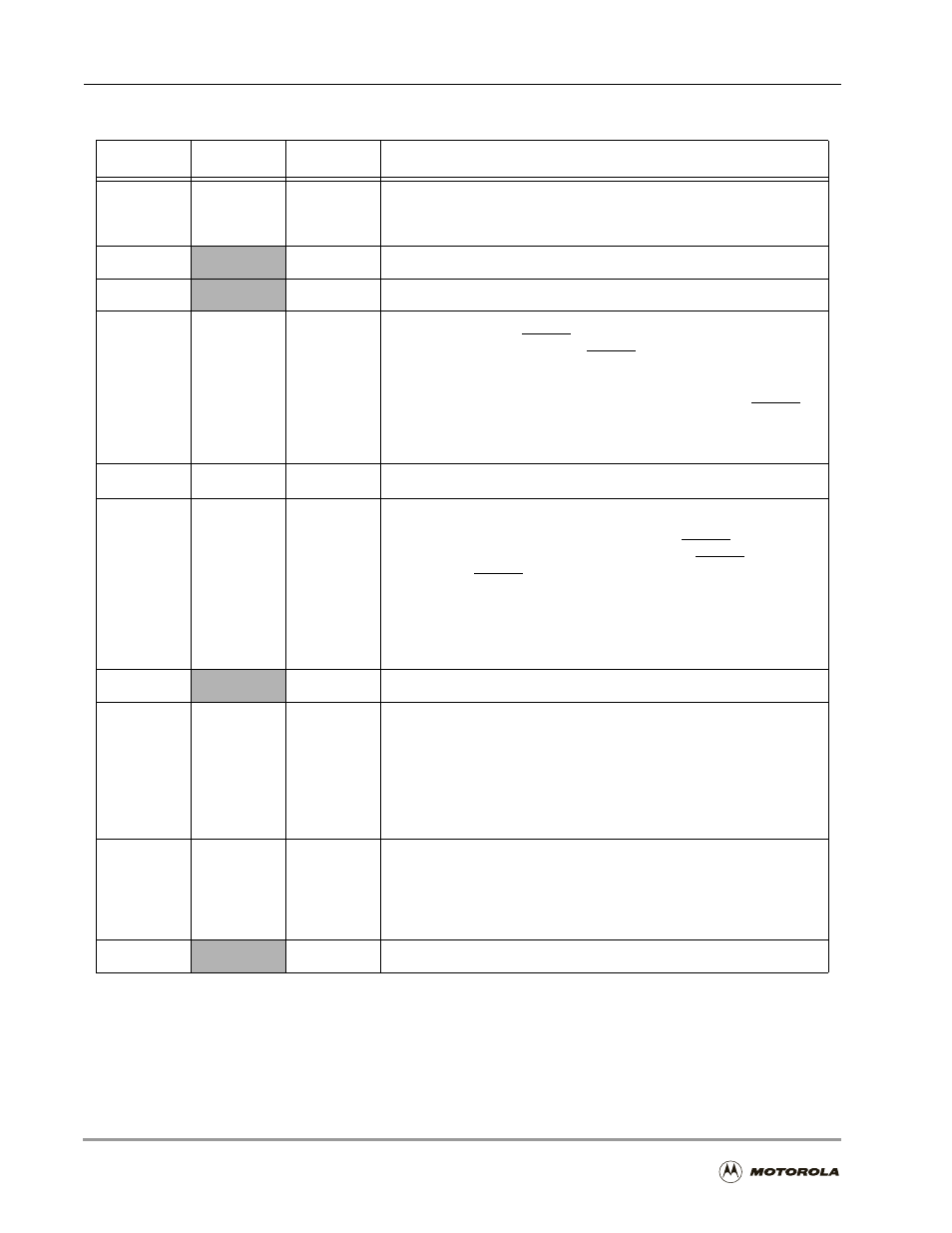

FBBC

0

Fast Back-to-Back Capable (hardwired to one)

Indicates that the HI32 supports fast back-to-back transactions as a

target in PCI mode (DCTR[HM]

=

$1). This bit is hardwired to one.

22–10

0

Reserved. Write to zero for future compatibility.

9

0

Not implemented. Write to zero for future compatibility.

8

SERE

0

System Error Enable

Enable/disables HI32 HSERR pin driving in PCI mode (DCTR[HM]

=

$1). When SERE is cleared, the HSERR pin is disabled (that is, high

impedance). When SERE is set, the force system error bit

DPCR[SERF] is set and the HI32 is an active PCI agent, or an address

parity error is detected, which causes the HI32 to pulse the HSERR pin

and set the signalled system error bit CSTR[SSE]. The personal

hardware reset clears SERE.

7

WCC

0

Wait Cycle Control (hardwired to zero)

6

PERR

0

Parity Error Response

Controls HI32 response to parity errors in PCI mode (DCTR[HM]

=

$1).

When PERR is cleared, the HI32 does not drive HPERR. If PERR is set

and a parity error is detected, the HI32 pulses the HPERR pin. If a

parity error or HPERR low is detected, the HI32 sets the DPR bit in the

CSTR/CCMR. In both cases, the HI32 sets bit 15 (DPE) in the

CSTR/CCMR, sets DPER in the DPSR, and generates a parity error

interrupt request if DPCR[PEIE] is set. The personal hardware reset

clears PERE.

5–3

0

Not implemented. Write to zero for future compatibility.

2

BM

0

Bus Master Enable

Controls HI32 ability to act as a master on the PCI bus in PCI mode

(DCTR[HM]

=

$1). When BM is cleared, the HI32 is disabled from acting

as a bus master; when BM is set, the HI32 can function as a bus

master. This bit affects the MARQ bit in the DSP-side Status Register

(DPSR). When BM is cleared, MARQ is also cleared. The personal

hardware reset clears BM.

1

MSE

0

Memory Space Enable

Controls the HI32 response to the PCI memory space accesses in PCI

mode (DCTR[HM]

=

$1). The HI32 memory space response is disabled

if MSE is cleared and enabled if MSE is set. The personal hardware

reset clears MSE.

0

0

Not implemented. Write to zero for future compatibility.

Table 6-26. Status/Command Configuration Register (CSTR/CCMR) Bit Definitions

Bit Number

Bit Name

Reset Value

Description