Motorola DSP56301 User Manual

Page 197

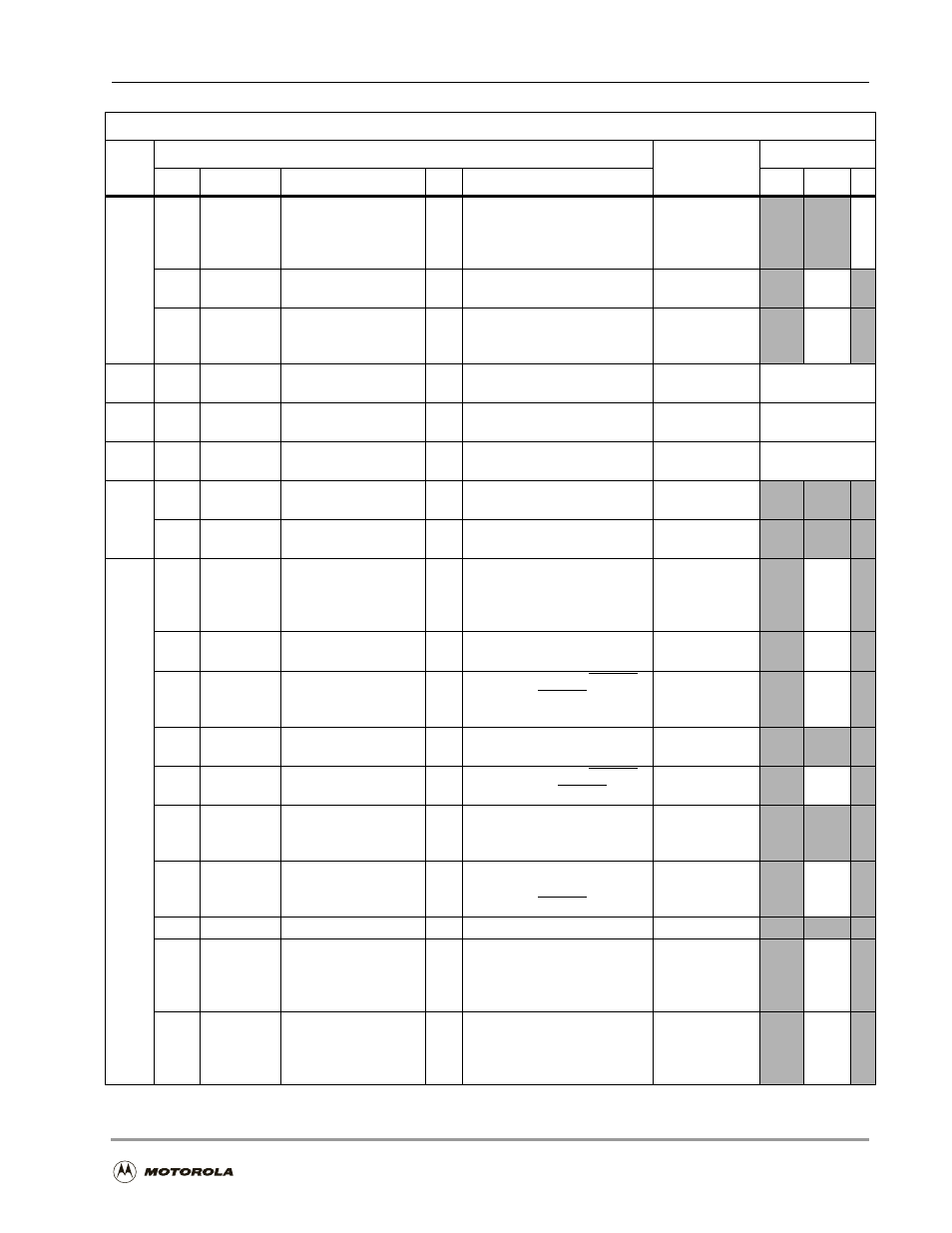

HI32 Programming Model/Quick Reference

Host Interface (HI32)

6

-79

HCVR

0

HC

Host Command

0

1

no host command pending

host command pending

cleared when

the HC interrupt

request is

serviced

-

-

0

7-1

HV[6–0]

Host Command Vector

default vector

-

default

vector

-

15

HNMI

Host Non Maskable

Interrupt Request

0

1

a maskable interrupt request

a non-maskable interrupt

request

-

0

-

HRXM

31-0

Host Master Receive

Data FIFO

empty

HRXS

31-0

Host Slave Receive

Data FIFO

empty

HTXR

31-0

Host Transmit Data

FIFO

empty

CVID

CDID

15-0

VID[15–0] Vendor ID

$

1057

hardwired $1057

-

-

-

31-16

DID[15–0] Device ID

$

1801

hardwired $1801

-

-

-

CCMR

CSTR

1

MSE

Memory Space Enable

0

1

memory space response

disabled

memory space response

enabled

-

0

-

2

BM

Bus Master Enable

0

1

HI32 PCI bus master disabled

HI32 PCI bus master enabled

-

0

-

6

PERR

Parity Error Response

0

1

HI32 does not drive HPERR

HI32 drives HPERR if a parity

error is detected

-

0

-

7

WCC

Wait Cycle Control

0

HI32 never executes address

stepping

hardwired 0

-

-

-

8

SERE

System Error Enable

0

1

HI32 does not drive HSERR

HI32 can drive HSERR

-

0

-

23

FBBC

Fast Back-to-Back

Capable

1

HI32 supports fast

back-to-back transactions as

a target

hardwired 1

-

-

-

24

DPR

Data Parity Reported

0

1

no parity error detected

HI32 master parity error

detected or HPERR asserted

cleared by

writing 1

-

0

-

26-25

DST[1–0] DEVSEL Timing

01 medium DEVSEL timing

hardwired 01

-

-

-

27

STA

Signaled Target Abort

0

1

HI32 has not generated a

target-abort event

HI32 target, generated a

target-abort event

cleared by

writing 1

-

0

-

28

RTA

Received Target Abort

0

1

HI32 has not received a

target-abort event

HI32 master, received a

target-abort event

cleared by

writing 1

-

0

-

HI32 Registers—Quick Reference

Reg

Bit

Comments

Reset Type

Num

Mnemonic

Name

Val

Function

HS

PH

PS