Motorola DSP56301 User Manual

Page 154

HI32 DSP-Side Programming Model

6

-36

DSP56301 User’s Manual

5–3

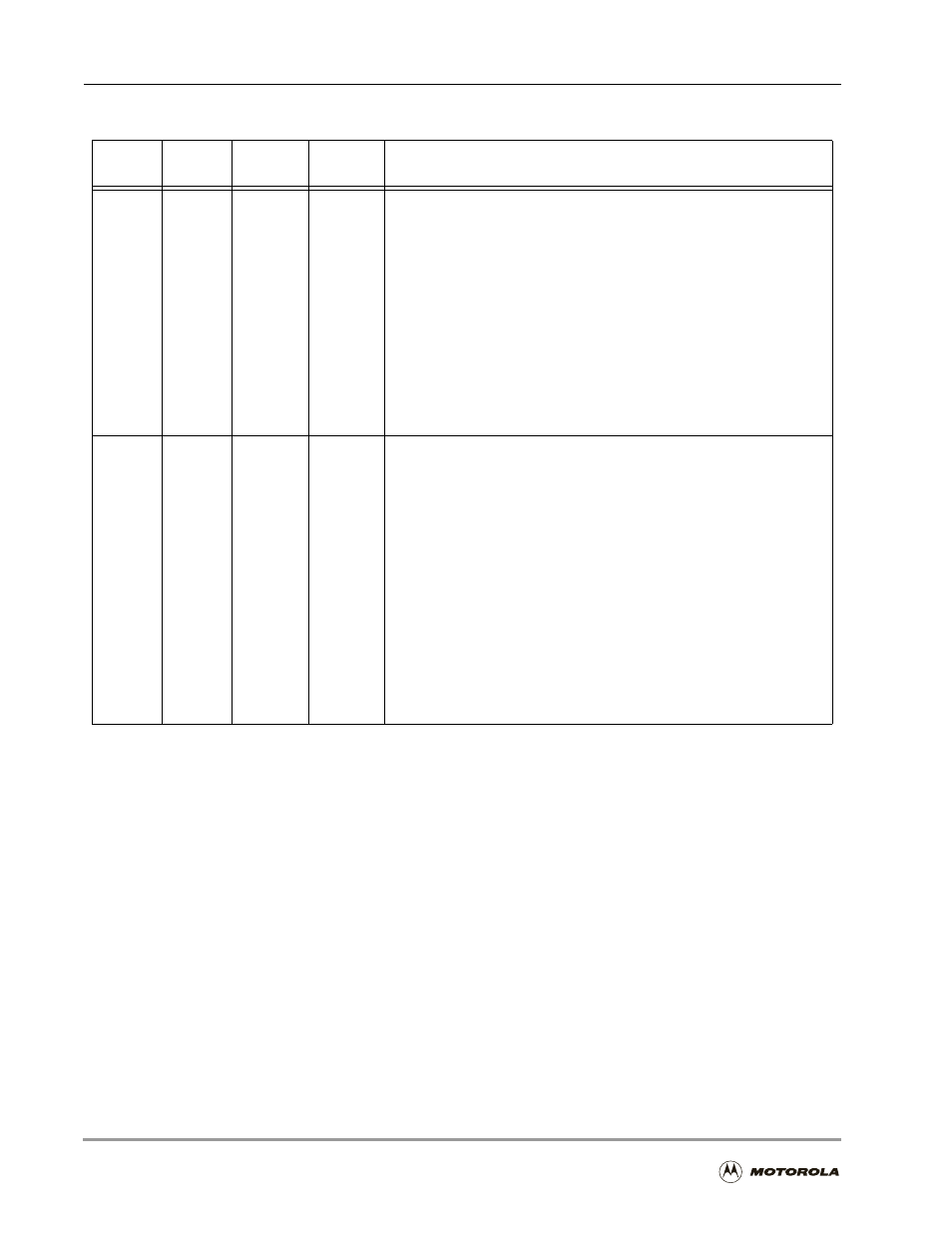

HF[2–0]

0

UBM

PCI

Host Flags

Indicate the state of host flags HF[2–0], respectively, in the Host Control

Register (HCTR) on the host side. Only the host processor can change

HF[2–0]. In PCI mode (DCTR[HM] = $1), the HF[2–0] bits are updated

at the end of a transaction. Personal hardware reset clears HF[2–0].

Note:

A potential problem exists when the status bits HF[2–0] are

read as an encoded triad. During personal hardware reset,

these bits are cleared asynchronously. For example: If

HF[2–0] change from 111 to 000, there is a small probability

the DSP56300 core could read the bits during transition and

receive 001 or 110 or other combinations instead of 000. To

avoid this problem, the DSP56300 core must read these bits

twice and check for consensus.

2

SRRQ

0

UBM

PCI

Slave Receive Data Request

Indicates that the receive data FIFO (DRXR) contains data written by

the host processor to the HI32 slave. When an external host writes data

to the host-to-DSP FIFO (HTXR-DRXR), SRRQ is set. SRRQ is cleared

when the DRXR is emptied by DSP56300 core reads or the data to be

read from the DRXR is master data. When SRRQ is set:

n

If SRIE is set, a slave receive data interrupt request is generated.

n

If enabled by an DSP56300 core DMA channel, a slave receive

data DMA request is generated.

Note:

Side-effects of reading the empty DRXR: If the DSP56300

core reads the DRXR when the FIFO is empty, the SRRQ bit is

set. SRRQ can also be set when the OncE interface reads it

(or when debugging tools are used). When the DRXR is read

while empty, either a reset or approximately 12 more reads of

DRXR are required to clear SRRQ.

Table 6-14. DSP Status Register (DSR) Bit Definitions (Continued)

Bit

Number

Bit Name

Reset

Value

Mode

Description