6 interrupt and mode control, Interrupt and mode control -9, Table 2-9 – Motorola DSP56301 User Manual

Page 39: 6 interrupt and mode control

Interrupt and Mode Control

Signals/Connections

2

-9

2.6

Interrupt and Mode Control

The interrupt and mode control signals select the chip’s operating mode as it comes out of

hardware reset. After

RESET

is deasserted, these inputs are hardware interrupt request lines.

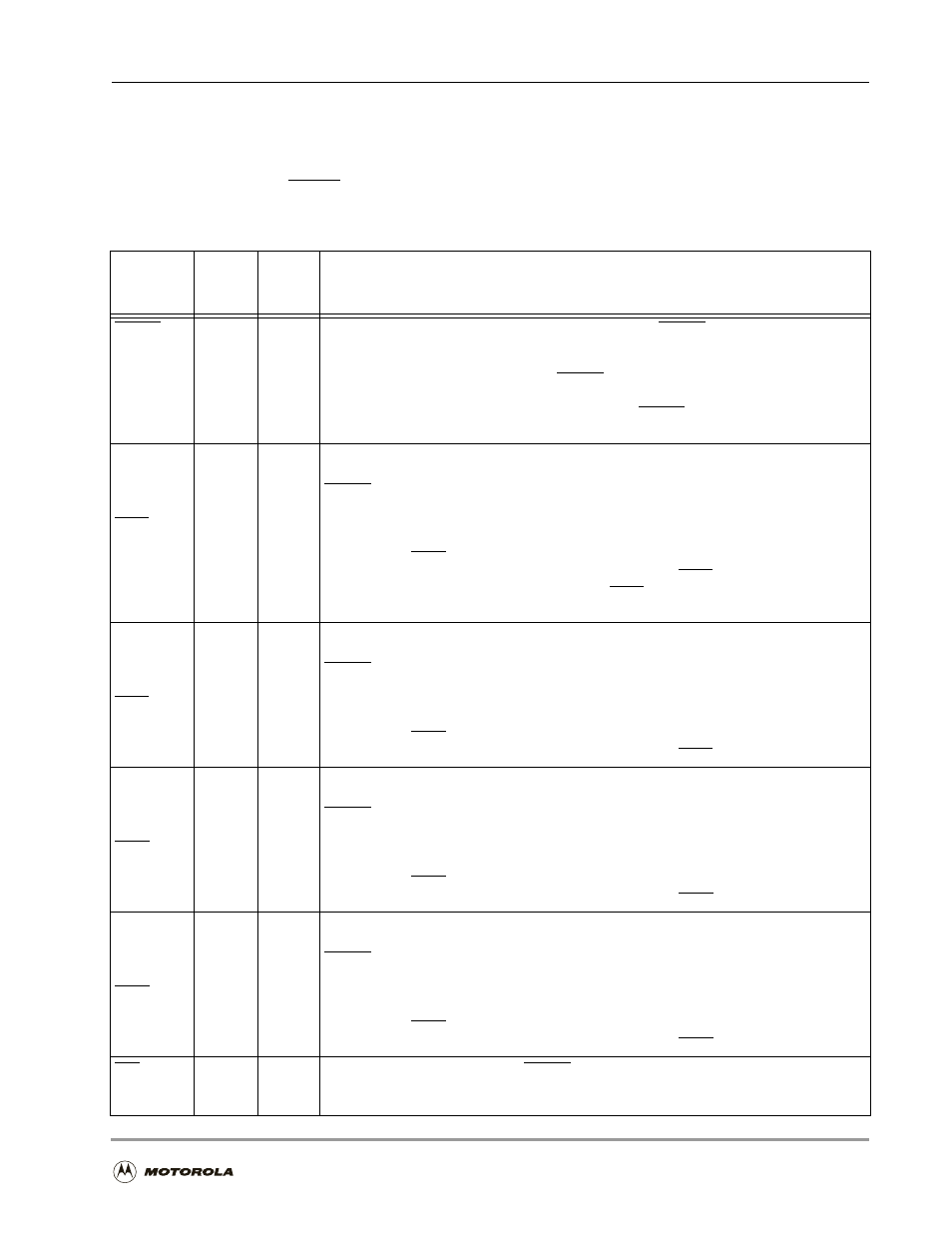

Table 2-9. Interrupt and Mode Control

Signal

Name

Type

State

During

Reset

Signal Description

RESET

Input,

Schmitt-

trigger

Input

Reset—Must be asserted at power up. Deassertion of RESET is internally synchronized

to CLKOUT. When asserted, the chip goes into the Reset state and the internal phase

generator is reset. The Schmitt-trigger allows a slowly rising input (such as aa charging

capacitor) to reset the chip reliably. If RESET is deasserted synchronous to CLKOUT,

exact start-up timing is guaranteed, allowing multiple processors to start synchronously

and operate together in

lock-step. Deasserting the RESET signal latches the initial chip

operating mode from the MODA–MODD inputs. This input is 5 V tolerant.

MODA

IRQA

Input,

Schmitt-

trigger

Input

Input

Mode Select A—Internally synchronized to CLKOUT. MODA, MODB, MODC, and

MODD select one of 16 initial chip operating modes, latched into the OMR when the

RESET signal is deasserted.

External Interrupt Request A—After reset, this input becomes a level-sensitive or

negative-edge-triggered, maskable interrupt request input during normal instruction

processing. If IRQA is asserted synchronous to CLKOUT, multiple processors can be

resynchronized using the WAIT instruction and asserting IRQA to exit the wait state. If

the processor is in the stop standby state and IRQA is asserted, the processor exits the

stop state.

MODB

IRQB

Input,

Schmitt-

trigger

Input

Input

Mode Select B—Internally synchronized to CLKOUT. MODA, MODB, MODC, and

MODD select one of 16 initial chip operating modes, latched into the OMR when the

RESET signal is deasserted.

External Interrupt Request B—After reset, this input becomes a level-sensitive or

negative-edge-triggered, maskable interrupt request input during normal instruction

processing. If IRQB is asserted synchronous to CLKOUT, multiple processors can be

resynchronized using the WAIT instruction and asserting IRQB to exit the wait state.

MODC

IRQC

Input,

Schmitt-

trigger

Input

Input

Mode Select C—Internally synchronized to CLKOUT. MODA, MODB, MODC, and

MODD select one of 16 initial chip operating modes, latched into the OMR when the

RESET signal is deasserted.

External Interrupt Request C—After reset, this input becomes a level-sensitive or

negative-edge-triggered, maskable interrupt request input during normal instruction

processing. If IRQC is asserted synchronous to CLKOUT, multiple processors can be

resynchronized using the WAIT instruction and asserting IRQC to exit the wait state.

MODD

IRQD

Input,

Schmitt-

trigger

Input

Input

Mode Select D—Internally synchronized to CLKOUT. MODA, MODB, MODC, and

MODD select one of 16 initial chip operating modes, latched into the OMR when the

RESET signal is deasserted.

External Interrupt Request D—After reset, this input becomes a level-sensitive or

negative-edge-triggered, maskable interrupt request input during normal instruction

processing. If IRQD is asserted synchronous to CLKOUT, multiple processors can be

resynchronized using the WAIT instruction and asserting IRQD to exit the wait state.

NMI

Input,

Schmitt-

trigger

Input

Nonmaskable Interrupt—After RESET deassertion and during normal instruction

processing, the negative-edge-triggered NMI request is internally synchronized to

CLKOUT.