4 watchdog modes, 1 watchdog pulse (mode 9), Watchdog modes -22 – Motorola DSP56301 User Manual

Page 284: Watchdog pulse (mode 9) -22, 4 watchdog modes, The following watchdog timer modes are provided, Watchdog pulse, Signal is generated when the

Operating Modes

9

-22

DSP56301 User’s Manual

9.3.4

Watchdog Modes

The following watchdog timer modes are provided:

n

Watchdog Pulse

n

Watchdog Toggle

9.3.4.1 Watchdog Pulse (Mode 9)

In Mode 9, the timer generates an external signal at a preset rate. The signal period is equal to

the period of one timer clock. After the counter reaches the value in the TCPR, if the

TCSR[TRM] bit is set, the counter is loaded with the TLR value on the next timer clock and

the count resumes. Therefore TRM = 1 is not useful for watchdog functions. If the

TCSR[TRM] bit is cleared, the counter continues to increment on each subsequent timer

clock. This process repeats until the timer is disabled (that is, TCSR[TE] is cleared). If the

counter overflows, a pulse is output on the

TIO

signal with a pulse width equal to the timer

clock period. If the INV bit is set, the pulse polarity is high (logical 1). If INV is cleared, the

pulse polarity is low (logical 0). The counter reloads when the TLR is written with a new

value while the TCSR[TE] bit is set. In Mode 9, internal logic preserves the

TIO

value and

direction for an additional 2.5 internal clock cycles after the hardware

RESET

signal is

asserted. This convention ensures that a valid

RESET

signal is generated when the

TIO

signal

resets the DSP56301.

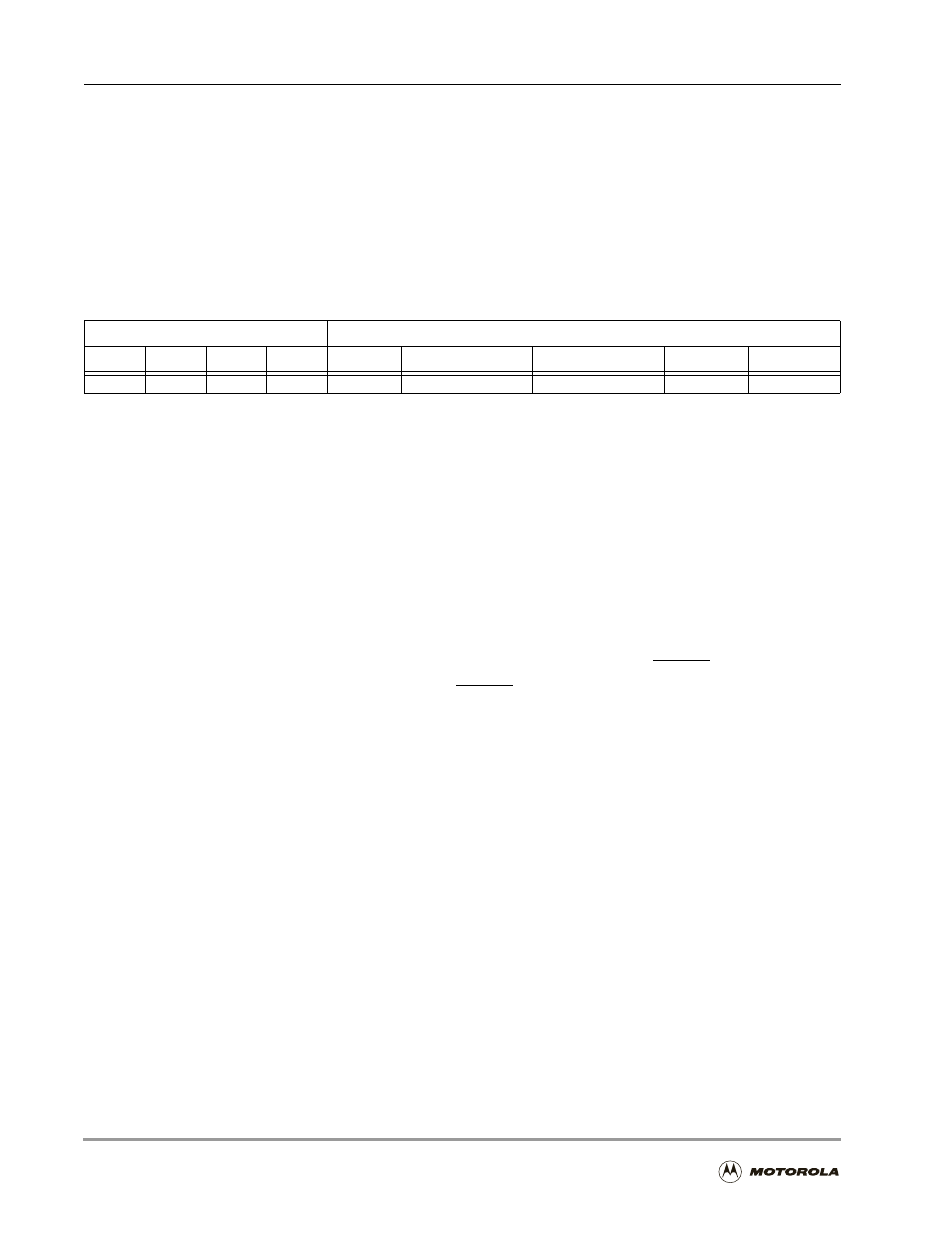

Bit Settings

Mode Characteristics

TC3

TC2

TC1

TC0

Mode

Name

Function

TIO

Clock

1

0

0

1

9

Pulse

Watchdog

Output

Internal