Motorola DSP56301 User Manual

Page 176

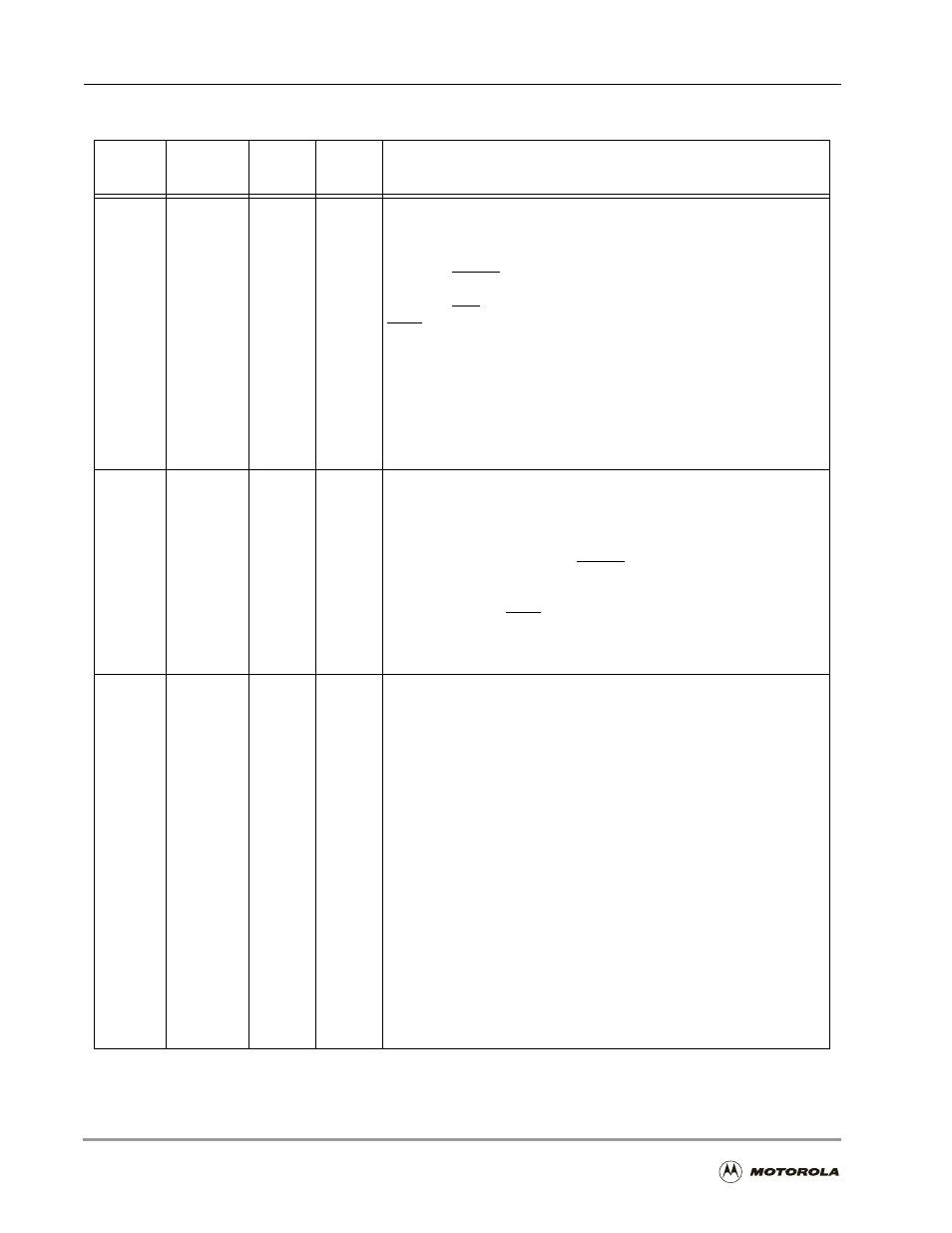

Host-Side Programming Model

6

-58

DSP56301 User’s Manual

2

HRRQ

0

UBM

PCI

Host Receive Data Request

Indicates that the host slave receive data FIFO (HRXS) contains data

from the DSP56300 core and can be read by the host processor. In PCI

mode, as a target in a read data phase from the HRXS, the HI32

deasserts HTRDY and inserts up to eight PCI wait cycles, if HRRQ is

cleared. In a Universal Bus mode read from the HRXS, the HI32 slave

deasserts HTA as long as HRRQ is cleared. HRRQ can assert the

HIRQ pin if the RREQ bit is set. Regardless of whether the HRRQ host

interrupt request is enabled, HRRQ provides valid status so that the

host processor can use polling techniques. HRRQ functions in

accordance with the value of the slave fetch type (SFT) bit in the HCTR.

In Fetch mode, (SFT = 1), the HRRQ is always read as zero. In

Pre-Fetch mode (SFT = 0), the DSP-to-host data path is FIFO buffered.

HRRQ reflects the status of the HRXS. HRRQ is cleared if the HRXS is

empty and is set when data is transferred from the DTXS.

1

HTRQ

0

UBM

PCI

Host Transmit Data Request

Indicates that the host transmit data FIFO (HTXR) is not full and can be

written by the host processor. HTRQ is set when the HTXR data is

transferred to the DRXR. HTRQ is cleared when the HTXR is filled by

host processor writes. In PCI mode, as target in a write data phase to

the HTXR, the HI32 deasserts HTRDY, and inserts up to eight PCI wait

cycles, if HTRQ is cleared. In a Universal Bus mode write to the HTXR,

the HI32 slave deasserts HTA as long as HTRQ is cleared. HTRQ can

assert the external HIRQ pin if the TREQ bit is set. Regardless of

whether the HTRQ host interrupt request is enabled, HTRQ provides

valid status so that the host processor can use polling techniques.

0

TRDY

1

UBM

PCI

Transmitter Ready

Indicates that both HTXR and DRXR are empty. When TRDY is set to

one, both HTXR and DRXR are empty. TRDY is cleared when the host

processor writes to HTXR.

The data the host processor writes to the HTXR is immediately

transferred to the DSP side of the HI32. This has many applications.

For example, if the host processor issues a host command that causes

the DSP56300 core to read the DRXR, the host processor can be

guaranteed that the data it transferred to the HI32 is what the

DSP56300 core is receiving. To support high-speed data transfers, the

HI32 host-to-DSP data path is a six word deep FIFO (five words deep in

the Universal Bus modes, three word deep in 32-bit mode, DCTR[HM] =

$1 and HCTR[HTF] = $0). In PCI data transfers with DCTR[HM]

=

$1

and HCTR[HTF]

≠

$0, if TRDY is set, the HI32 does not insert wait states

into the next six data transfers written by the host to the HTXR. In PCI

data transfers with DCTR[HM] = $1 and HCTR[HTF] = $0 (that is, 32-bit

mode), if TRDY is set, the HI32 does not insert wait states in the next

three data phases written by the host to the HTXR. In Universal bus

mode data transfers, if TRDY is set, the HI32 does not insert wait states

into the next five data transfers written by the host to the HTXR.

Table 6-23. Host Interface Status Register (HSTR) Bit Definitions (Continued)

Bit

Number

Bit Name

Reset

Value

Mode

Description