Motorola DSP56301 User Manual

Page 37

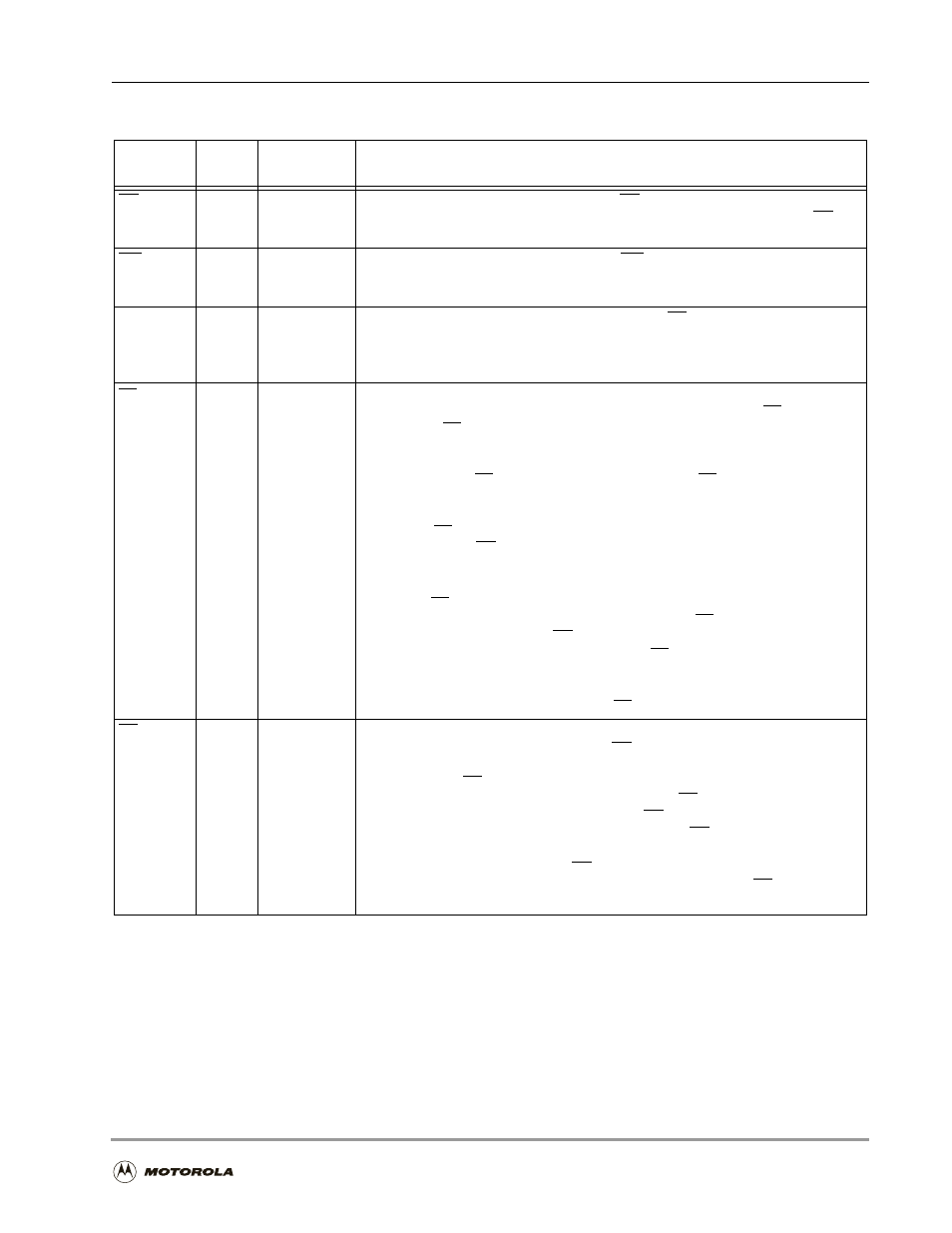

External Memory Expansion Port (Port A)

Signals/Connections

2

-7

RD

Output

Tri-stated

Read—When the DSP is the bus master, RD is an active-low output that is

asserted to read external memory on the data bus (D0–D23). Otherwise, RD is

tri-stated.

WR

Output

Tri-stated

Write—When the DSP is the bus master, WR is an active-low output that is

asserted to write external memory on the data bus (D0–D23). Otherwise, the

signals are tri-stated.

BS

Output

Tri-stated

Bus Strobe — When the DSP is the bus master, BS is asserted for half a clock

cycle at the start of a bus cycle to provide an “early bus start” signal for a bus

controller. If the external bus is not used during an instruction cycle, BS remains

deasserted until the next external bus cycle.

TA

Input

Ignored Input

Transfer Acknowledge—If the DSP56301 is the bus master and there is no

external bus activity, or the DSP56301 is not the bus master, the TA input is

ignored. The TA input is a data transfer acknowledge (DTACK) function that can

extend an external bus cycle indefinitely. Any number of wait states (1,

2. . .infinity) may be added to the wait states inserted by the bus control register

(BCR) by keeping TA deasserted. In typical operation, TA is deasserted at the

start of a bus cycle, is asserted to enable completion of the bus cycle, and is

deasserted before the next bus cycle. The current bus cycle completes one clock

period after TA is asserted synchronous to CLKOUT. The number of wait states is

determined by the

TA

input or by the BCR, whichever is longer. The BCR can be

used to set the minimum number of wait states in external bus cycles.

To use the TA functionality, the BCR must be programmed to at least one wait

state. A zero wait state access cannot be extended by TA deassertion; otherwise,

improper operation may result.

TA

can operate synchronously or asynchronously

depending on the setting of the OMR[TAS] bit. TA functionality must not be used

while DRAM accesses are performed; otherwise, improper operation may result.

Note: For operations that do not use the TA bus control function, pull this pin low.

BR

Output

Output

(deasserted)

Bus Request—Asserted when the DSP requests bus mastership and deasserted

when the DSP no longer needs the bus. BR is asserted or deasserted

independently of whether the DSP56301 is a bus master or a bus slave. Bus

“parking” allows BR to be deasserted even though the DSP56301 is the bus

master. (See the description of bus “parking” in the BB signal description.) The

bus request hold (BRH) bit in the BCR allows BR to be asserted under software

control even though the DSP does not need the bus. BR is typically sent to an

external bus arbitrator that controls the priority, parking, and tenure of each

master on the same external bus. BR is affected only by DSP requests for the

external bus, never for the internal bus. During hardware reset, BR is deasserted

and the arbitration is reset to the bus slave state.

Table 2-8. External Bus Control Signals (Continued)

Signal

Name

Type

State During

Reset

Signal Description