2 overview, Overview -4, 2 overview – Motorola DSP56301 User Manual

Page 122

Overview

6

-4

DSP56301 User’s Manual

6.2

Overview

Figure 6-1 shows the two banks of registers in the HI32, DSP-side and host-side. The

DSP56300 core can access the DSP-side registers, which are listed in Table 6-9, HI32

Programming Model, DSP Side, on page 6-22. The host-side registers, which are accessed by

the host bus, are listed in Table 6-17, HI32 Programming Model, Host-Side Registers, on

page 6-44.

Output Data

Alignment

24-bit words to 32-bit words:

n

Left aligned and zero filled

n

Right aligned and zero extended

n

Right aligned and sign extended

24-bit words to 16-bit words (two most significant

bytes, two least significant bytes)

Data

Tramsfer

Speed

n

Up to 33 Mword/sec zero wait-state data

transfers (with a 33 MHz PCI clock and a

DSP clock (CLKOUT) frequency of 66 MHz

or more)

n

True 32-bit input and output data transfers

(32-bit PCI bus data to two DSP56300 core

16-bit words, and

vice versa)

n

Bursts of up to 16384 32-bit words when

accessed as a memory-mapped target

n

Bursts of up to sixty-four 32-bit words or

unlimited length (as master)

n

High speed (fast peripheral) DSP56300

core DMA transfers (two core clock cycles

per DMA transfer)

n

Data transfers at three clock cycles per

transfer (that is, 22 Mword/sec for a 66 MHz

DSP clock (CLKOUT)), when operating

synchronously with an DSP56300

core-based DSP host (two wait states per

access)

n

High speed (fast peripheral) DSP56300

core DMA transfers (two core clock cycles

per DMA transfer)

Interrupts

n

Software-driven PCI Interrupt Requests

(Interrupt A)

n

Vectored DSP56300 core interrupts;

separately for receive, transmit, transaction

termination, error events, and host

commands

n

Interrupt requests: hardware driven (HIRQ)

and software driven (HINTA)

n

Vectored DSP56300 core interrupts;

separately for receive and transmit events

and host commands

Voltage

Both 3.3 V and 5 V PCI signalling environments

An external data buffer may be needed for drive

and voltage level compatibility with the external

bus (for example, the ISA bus requires buffering)

System

n

Memory-space and configuration

transactions as a target; memory-space,

I/O-space, and configuration transactions

as an initiator

n

Exclusive (locked) accesses

n

Self-Configuration mode for initializing the

configuration registers in a system without

an external system configurator

n

Address insertion in the data written to the

HI32

n

Parity generation, detection, and reporting

n

System error generation and reporting

n

Self-Configuration mode for initializing the

configuration registers in a system without

an external system configurator

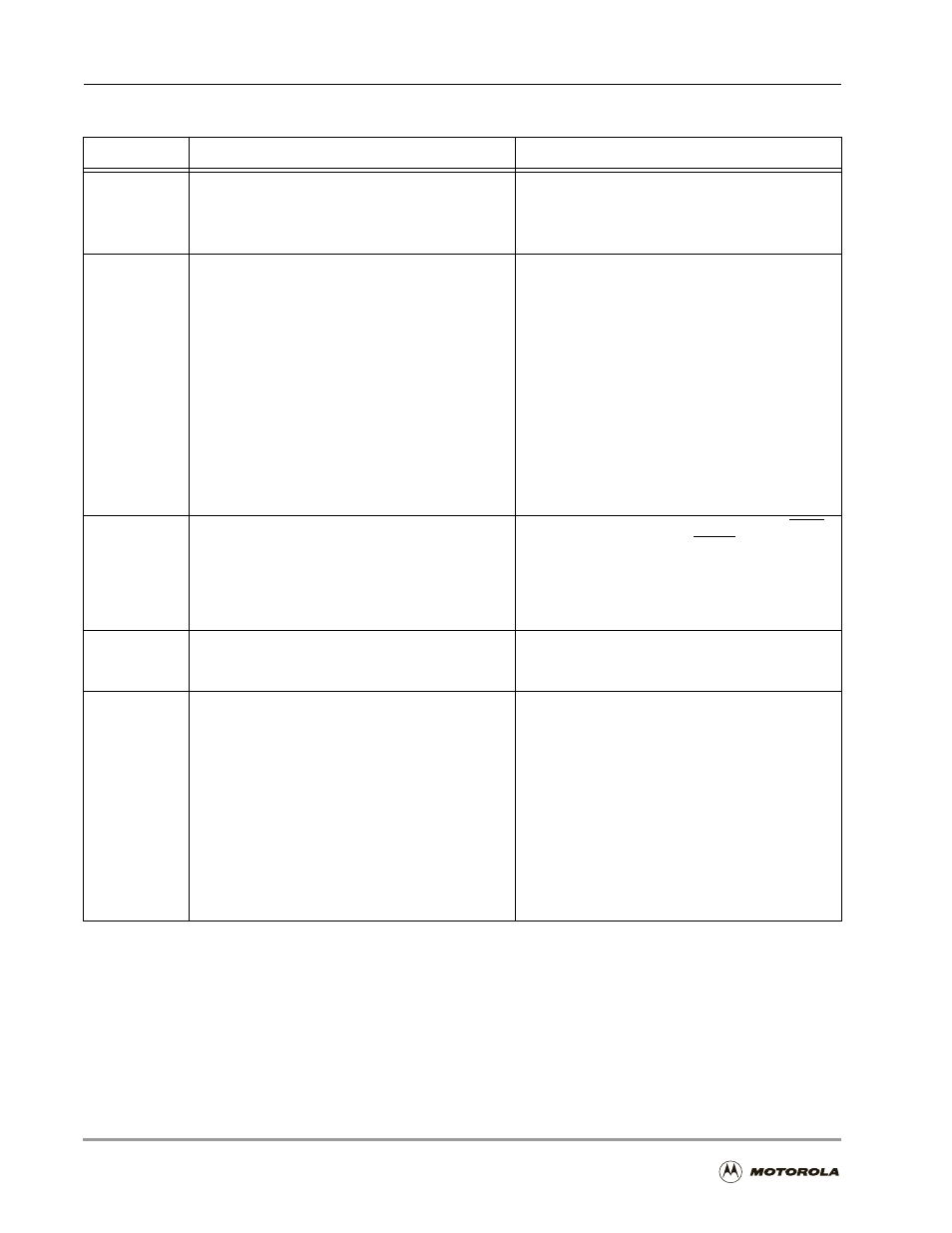

Table 6-2. HI32 Features in PCI Mode and Universal Bus Mode (Continued)

Feature

PCI Mode

Universal Bus Mode