1 terminate and reset (dctr[hm] = $0), 2 pci mode (dctr[hm] = $1), Terminate and reset (dctr[hm] = $0) -13 – Motorola DSP56301 User Manual

Page 131: Pci mode (dctr[hm] = $1) -13, Hi32 modes -13, 1 terminate and reset (dctr[hm] = $0), 2 pci mode (dctr[hm] = $1)

DSP-Side Operating Modes

Host Interface (HI32)

6

-13

6.5.1

Terminate and Reset (DCTR[HM] = $0)

When DCTR[HM2–0] is written with a value of $0 and the HI32 is in PCI mode (DCTR[HM]

= $1), the HI32 is an active PCI master. The HI32 generates a master-initiated termination. If

it is a selected target in a memory space transaction, the HI32 generates a

target-disconnect-C/retry event, thus completing the PCI transaction. When the PCI idle state

is subsequently detected, the HI32 clears DSR[HACT] and enters the personal software reset

state. In personal software reset state, all data paths are cleared, and the HI32 responds to all

memory and configuration space transactions with a retry event. If the HI32 is not in an active

target in PCI mode (DCTR[HM]

≠

$1) memory space transaction, the HI32 immediately clears

DSR[HACT] in the DSR and enters the personal software (PS) reset state.

Clearing the DCTR[HM] bits does not affect configuration space transactions. In the personal

software reset the HI32 consumes very little current. This is a low-power state. For even

greater power savings, the HI32 can be programmed to the GPIO mode.

6.5.2

PCI Mode (DCTR[HM] = $1)

The HI32 supports:

n

Glueless connection to the standard PCI bus.

n

Operation as an initiator (master) or target (slave).

n

24- to 32-bit, 32- to 24-bit data formatting and true 32-bit (Dword) data transfers.

n

Memory-space and configuration transactions as a target.

n

Memory-space, I/O-space and configuration transactions as an initiator.

Note:

For proper operation ,

CLKOUT

should be 5/3 of the PCI clock.

Using DMA channels optimizes PCI data throughput, as Example 6-1 and Example 6-2

illustrate.

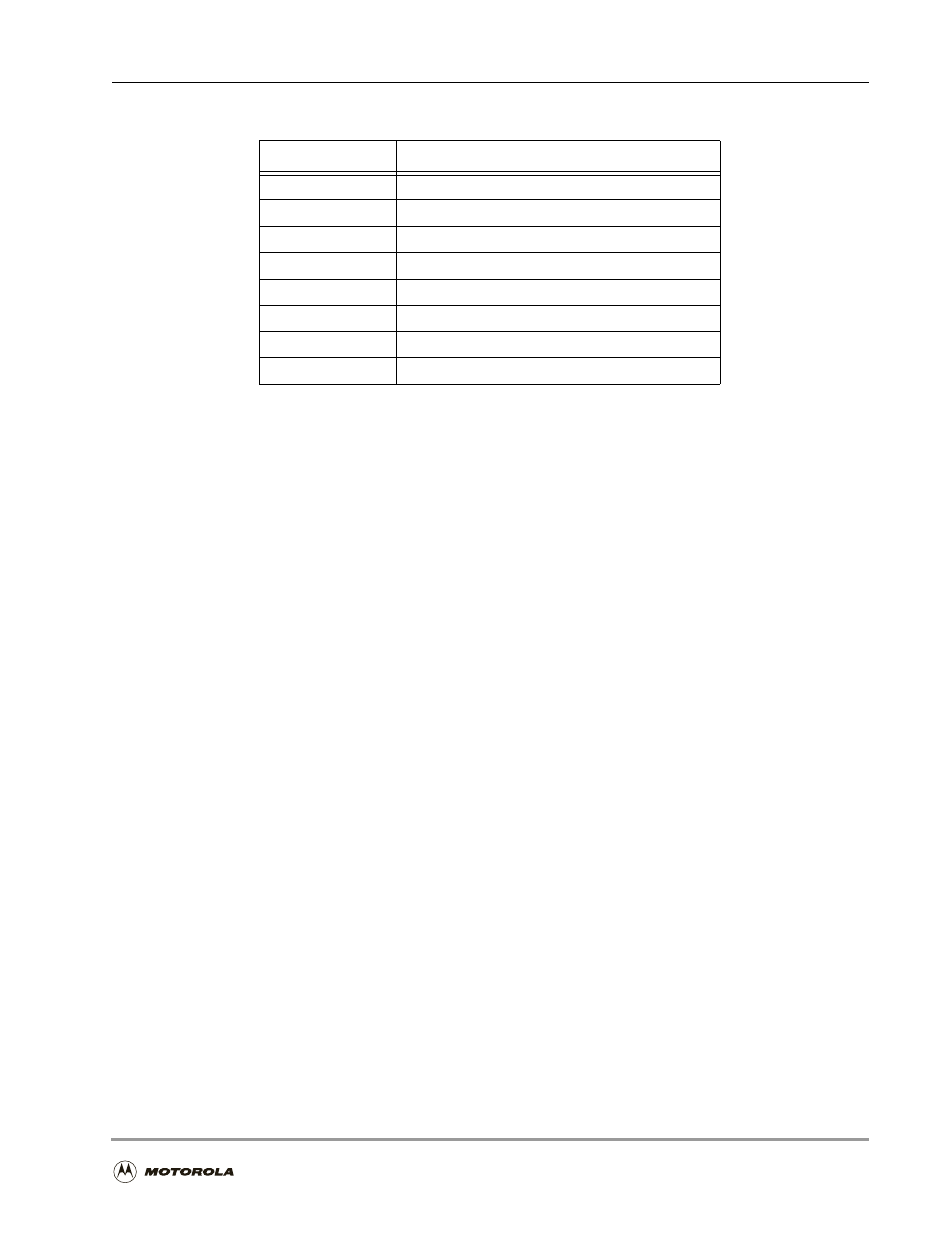

Table 6-7. HI32 Modes

HM[2–0]

HI32 Mode

000

Terminate and Reset

001

PCI

010

Universal Bus

011

Enhanced Universal Bus

100

GPIO

101

Self-Configuration

110

Reserved

111

Reserved