6 dsp pci status register (dpsr), Dsp pci status register (dpsr) -38, Dsp pci status register (dpsr) bit definitions -38 – Motorola DSP56301 User Manual

Page 156: 6 dsp pci status register (dpsr)

HI32 DSP-Side Programming Model

6

-38

DSP56301 User’s Manual

6.7.6

DSP PCI Status Register (DPSR)

.

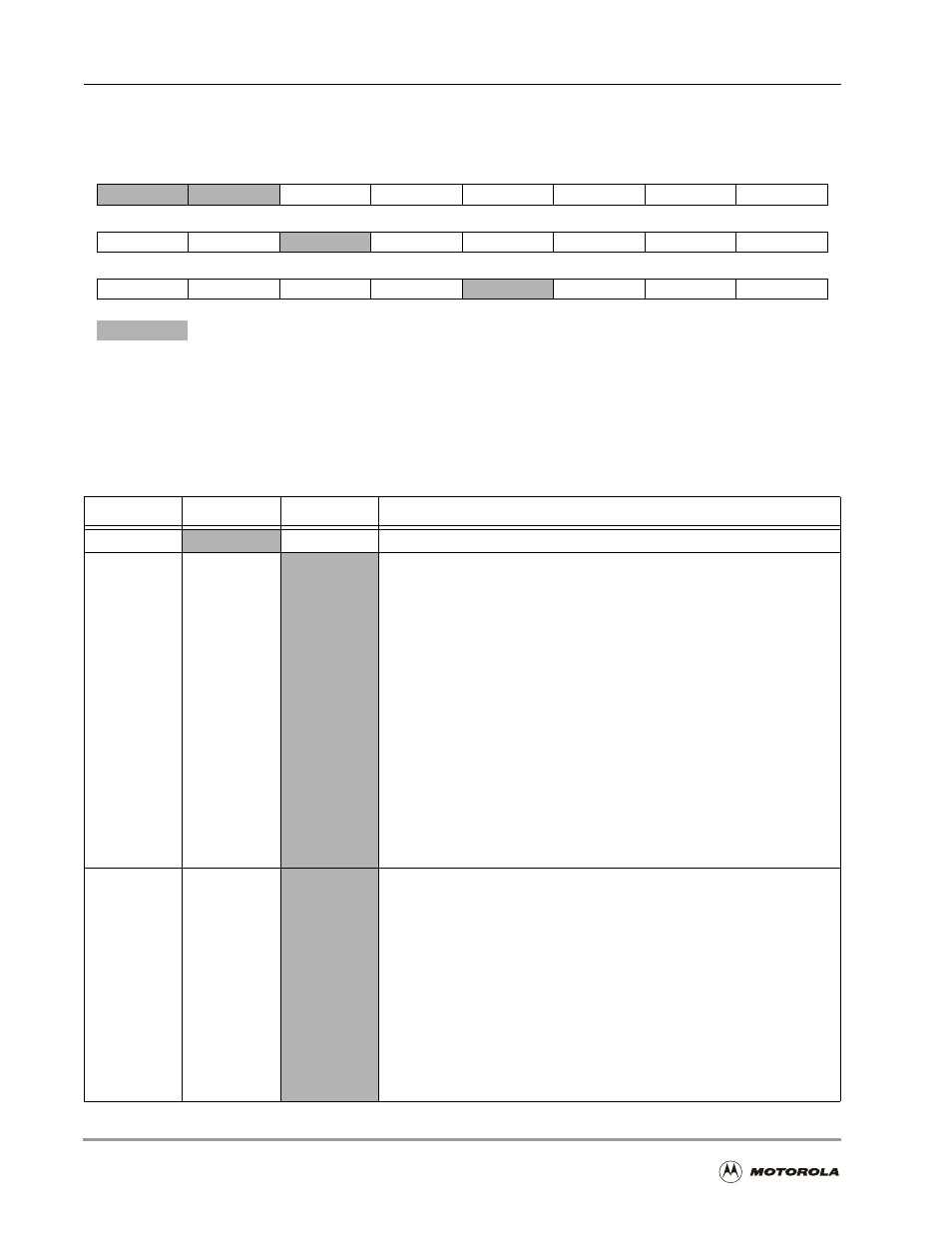

A 24-bit read-only status register by which the DSP56300 core examines the status and flags

of the HI32 in PCI mode (DCTR[HM]

=

$1). The host processor cannot access the DPSR.

23

22

21

20

19

18

17

16

RDC5

RDC4

RDC3

RDC2

RDC1

RDC0

15

14

13

12

11

10

9

8

RDCQ

MDT

HDTC

TO

TRTY

TDIS

TAB

7

6

5

4

3

2

1

0

MAB

DPER

APER

MARQ

MRRQ

MTRQ

MWS

Reserved. Write to 0 for future compatibility

Figure 6-10. DSP PCI Status Register (DPSR)

Table 6-15. DSP PCI Status Register (DPSR) Bit Definitions

Bit Number

Bit Name

Reset Value

Description

23–22

0

Reserved. Write to 0 for future compatibility.

21–16

RDC[5–0]

Remaining Data Count

Read-only bits that indicate the PCI data phases remaining to complete a

PCI burst after the HI32 completes a transaction as a PCI master.

RDC[5–0] are updated each time a transaction terminates and the HI32 is

a PCI master (MARQ = 1).

If the transaction terminates normally, the

value of RDC[5–0] is $00 and TO = 0, TRTY = 0, TDIS = 0, TAB = 0, MAB

= 0. If the master access counter is enabled and the burst does not

complete for any reason, the value of RDC[5–0] is the remaining number

of data phases remaining to complete the burst minus one (that is, RDC =

$2 signifies that three more words must be transferred to complete the

burst). The length of the burst is limited by BL[5–0] in the DPMC.

If the

master counter is disabled (DPCR[MACE] is cleared), the RDC[5–0] and

RDCQ bits are not valid.

Note:

Typical reasons why a burst does not complete are a

target-initiated transaction termination or a requirement that the

HI32 generate a master-initiated time-out transaction

termination.

15

RDCQ

Remaining Data Count Qualifier

Qualifies the value of the DPSR[RDC] bits. If the MDT bit is cleared

(MARQ = 1) at the end of a transaction initiated by the HI32 (that is, not all

the master data transferred), the burst length for the next transaction to

the same target to complete the data transfer is calculated as follows:

BL[5–0] = RDC[5–0] + RDCQ

Note:

If any of the DPSR[TAB/TRTY/MAB] status bits are set, the

transaction can be initiated again with the same address and

burst length by writing the DPAR with its previous value. If the

master counter is disabled (DPCR[MACE] is cleared), the

RDC[5–0] and RDCQ bits are not valid.