Motorola DSP56301 User Manual

Page 172

Host-Side Programming Model

6

-54

DSP56301 User’s Manual

6

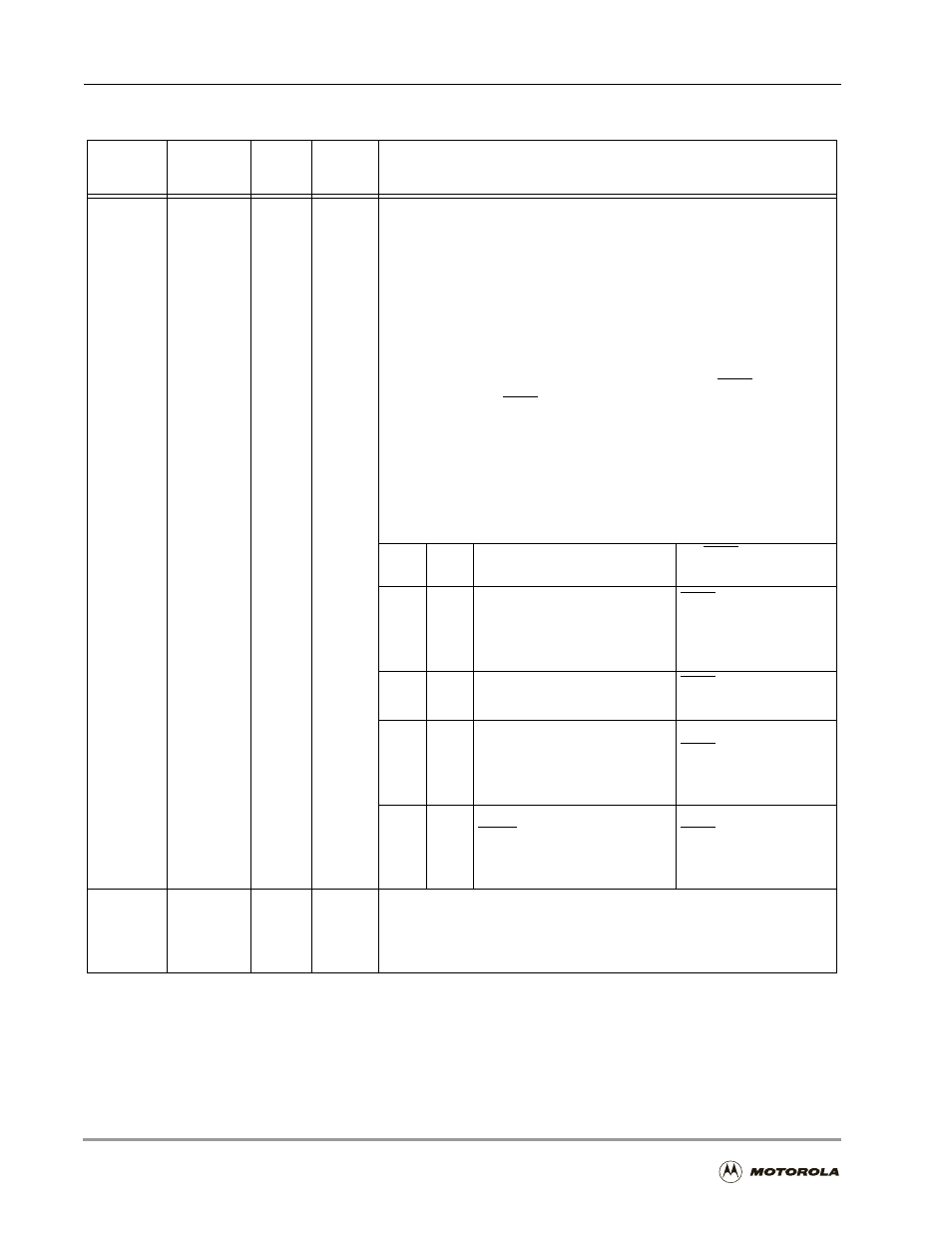

DMAE

0

UBM

DMA Enable (ISA/EISA)

Used by the host processor to enable the HI32 ISA/EISA DMA-type

accesses in a Universal Bus mode (DCTR[HM] = $2 or $3). If the host

drives the HAEN pin low, the HI32 responds when it identifies its address

(such as ISA/EISA I/O-type accesses). The HI32 does not respond to

ISA/EISA DMA-type accesses. When the HAEN pin is high:

n

If DMAE is cleared, the HI32 cannot be accessed.

n

If DMAE is set, the HI32 responds to ISA/EISA DMA-type

accesses.

When DMAE is cleared, the HDRQ pin is deasserted, HIRQ is active.

If DMAE is set, the HIRQ pin is deasserted, HDRQ is active. This allows

the HI32 to generate host DMA requests during ISA/EISA I/O-type

accesses. A typical application is an external host write to the HI32 using

a polling procedure and external DMA reads from the HI32. An external

bus controller arbitrates between the two and sets or clears HAEN

accordingly. If both DMAE and HAEN are set, HTA is released (high

impedance) because DMA devices cannot extend DMA cycles

(ISA/EISA). The personal hardware reset clears DMAE.

DMAE

bit

HAEN

pin

ISA/EISA Access Type

HIRQ and HDRQ

Functionality

0

0

The HI32 responds when it

identifies its address

(that is, ISA/EISA I/O-type

access)

HIRQ is active,

HDRQ is deasserted

0

1

The HI32 does not respond to

any access

HIRQ is active,

HDRQ is deasserted

1

0

The HI32 responds when it

identifies its address

(that is, ISA/EISA I/O-type

access)

HDRQ is active,

HIRQ is deasserted

1

1

1

The HI32 responds when

HDAK is asserted

(that is, ISA/EISA DMA-type

access)

HDRQ is active,

HIRQ is deasserted

5 –3

HF[2–0]

0

UBM

PCI

Host Flags

General-purpose flags for host-to-DSP communication. The host

processor sets and clears HF[2–0]. The personal hardware reset clears

HF[2–0].

Table 6-22. Host Interface Control Register (HCTR) Bit Definitions (Continued)

Bit

Number

Bit Name

Reset

Value

Mode

Description