Enhanced synchronous serial interface 0 -23, Table 2-13 – Motorola DSP56301 User Manual

Page 53

Enhanced Synchronous Serial Interface 0

Signals/Connections

2

-23

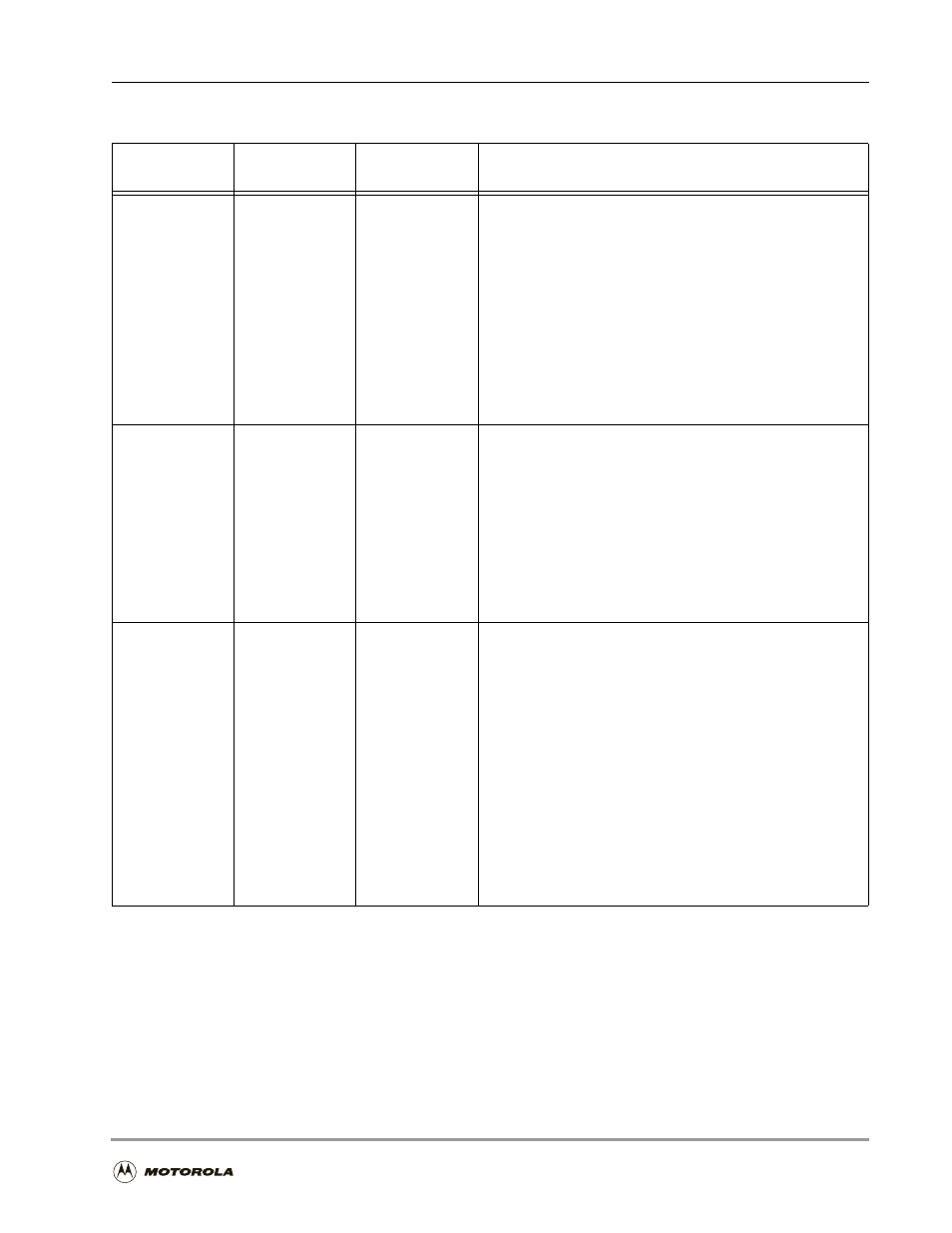

Table 2-13. Enhanced Synchronous Serial Interface 0

Signal Name

Type

State During

Reset

Signal Description

SC00

PC0

Input or Output

Input

Serial Control 0—For asynchronous mode, this signal is

used for the receive clock I/O (Schmitt-trigger input). For

synchronous mode, this signal is used either for transmitter 1

output or for serial I/O flag 0.

Port C 0—The default configuration following reset is GPIO

input PC0. When configured as PC0, signal direction is

controlled through the port directions register (PRR0). The

signal can be configured as ESSI signal SC00 through the

port control register (PCR0).

This signal has a weak keeper to maintain the last state even

if all drivers are tri-stated.

SC01

PC1

Input/

Output

Input or Output

Input

Serial Control 1—For asynchronous mode, this signal is the

receiver frame sync I/O. For synchronous mode, this signal is

used either for transmitter 2 output or for serial I/O flag 1.

Port C 1—The default configuration following reset is GPIO

input PC1. When configured as PC1, signal direction is

controlled through PRR0. The signal can be configured as an

ESSI signal SC01 through PCR0.

This signal has a weak keeper to maintain the last state even

if all drivers are tri-stated.

SC02

PC2

Input/

Output

Input or Output

Input

Serial Control Signal 2—Used for frame sync I/O. SC02 is

the frame sync for both the transmitter and receiver in

synchronous mode, and for the transmitter only in

asynchronous mode. When configured as an output, this

signal is the internally generated frame sync signal. When

configured as an input, this signal receives an external frame

sync signal for the transmitter (and the receiver in

synchronous operation).

Port C 2—The default configuration following reset is GPIO

input PC2. When configured as PC2, signal direction is

controlled through PRR0. The signal can be configured as an

ESSI signal SC02 through PCR0.

This signal has a weak keeper to maintain the last state even

if all drivers are tri-stated.