Motorola DSP56301 User Manual

Page 193

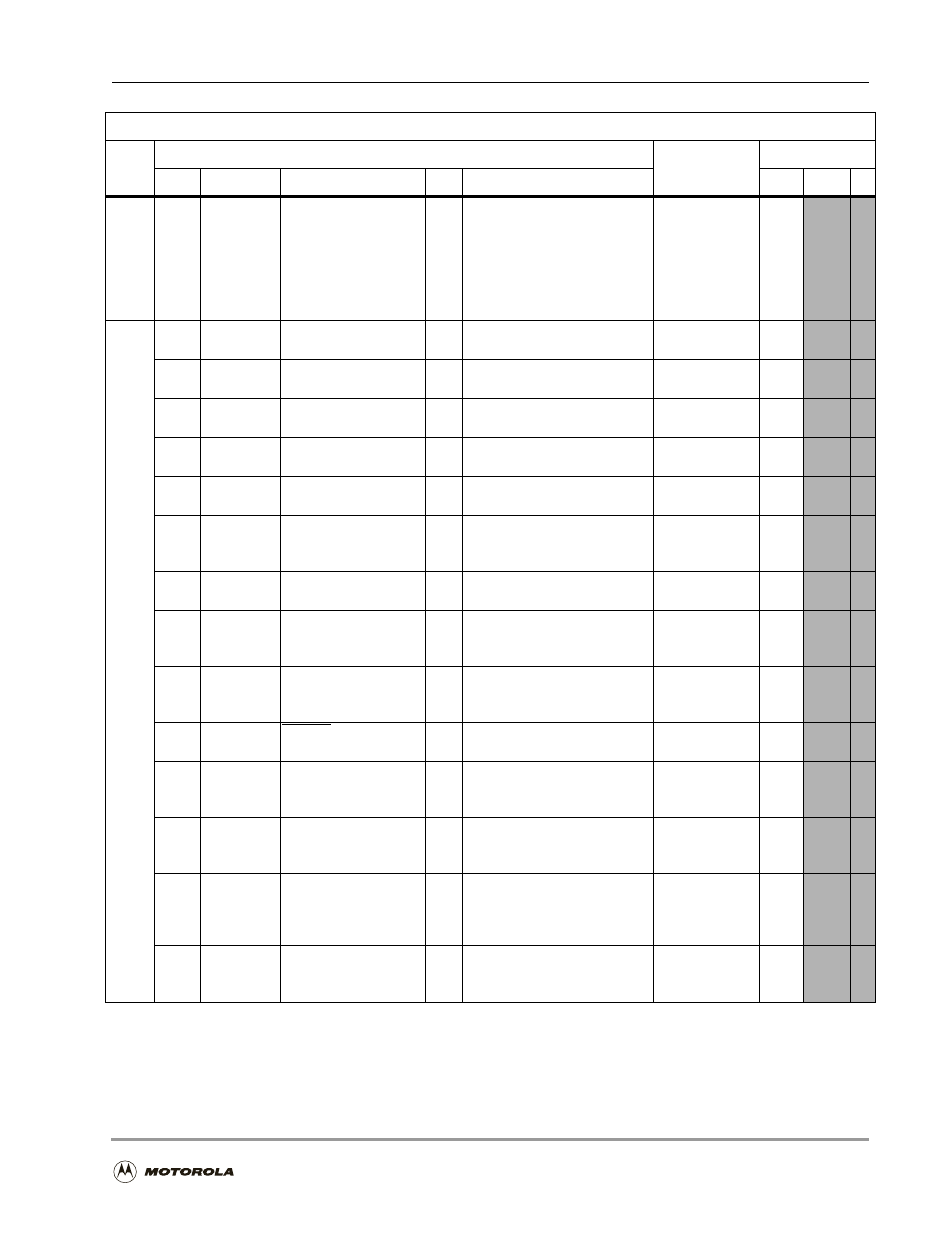

HI32 Programming Model/Quick Reference

Host Interface (HI32)

6

-75

DCTR

cont.

22-20

HM[2–0]

HI32 Mode

000

001

010

011

100

101

11x

Terminate and Reset

PCI

UBM

Enhanced UBM

GPIO

Self-Configuration

Reserved

changed to

non-zero value

only in PS reset

$0

-

-

DPCR

1

MTIE

Master Transmit

Interrupt Enable

0

1

MTRQ interrupt disabled

MTRQ interrupt enabled

0

-

-

2

MRIE

Master Receive

Interrupt Enable

0

1

MRRQ interrupt disabled

MRRQ interrupt enabled

0

-

-

4

MAIE

Master Address

Interrupt Enable

0

1

A/DPER interrupt disabled

A/DPER interrupt enabled

0

-

-

5

PEIE

Parity Error Interrupt

Enable

0

1

MARQ interrupt disabled

MARQ interrupt enabled

0

-

-

7

TAIE

Transaction Abort

Interrupt Enable

0

1

M/TAB interrupt disabled

M/TAB interrupt enabled

0

-

-

9

TTIE

Transaction

Termination Interrupt

Enable

0

1

TO/DIS/RTY interrupt

disabled

TO/DIS/RTY interrupt enabled

0

-

-

12

TCIE

Transfer Complete

Interrupt Enable

0

1

HDTC interrupt disabled

HDTC interrupt enabled

0

-

-

14

CLRT

Clear Transmitter

0

1

inactive

empty master transmitter path

set only if

hardware clears

MARQ = 1

0

-

-

15

MTT

Master Transfer

Terminate

0

1

inactive

terminate current PCI

transaction

set only if

hardware clears

MWS = 1

0

-

-

16

SERF

HSERR Force

0

1

inactive

generate a PCI system error

cleared by

hardware

0

-

-

18

MACE

Master Access

Counter Enable

0

1

unlimited burst length

burst length is limited by the

BL value

0

-

-

19

MWSD

Master Wait State

Disable

0

1

HI32 master inserts wait

states

HI32 master releases bus

set only if MARQ

= 1

0

-

-

20

RBLE

Receive Buffer Lock

Enable

0

1

HI32 responds to new

accesses

HI32 retries accesses after

write accesses

changed only in

PS reset

0

-

-

21

IAE

Insert Address Enable

0

1

HI32 does not insert address

HI32 inserts address in

incoming data

changed only in

PS reset

0

-

-

HI32 Registers—Quick Reference

Reg

Bit

Comments

Reset Type

Num

Mnemonic

Name

Val

Function

HS

PH

PS