2 timer prescaler load register (tplr), Timer prescaler load register (tplr) -27, 2 timer prescaler load register (tplr) – Motorola DSP56301 User Manual

Page 289

Triple Timer Module Programming Model

Triple Timer Module

9

-27

9.4.2

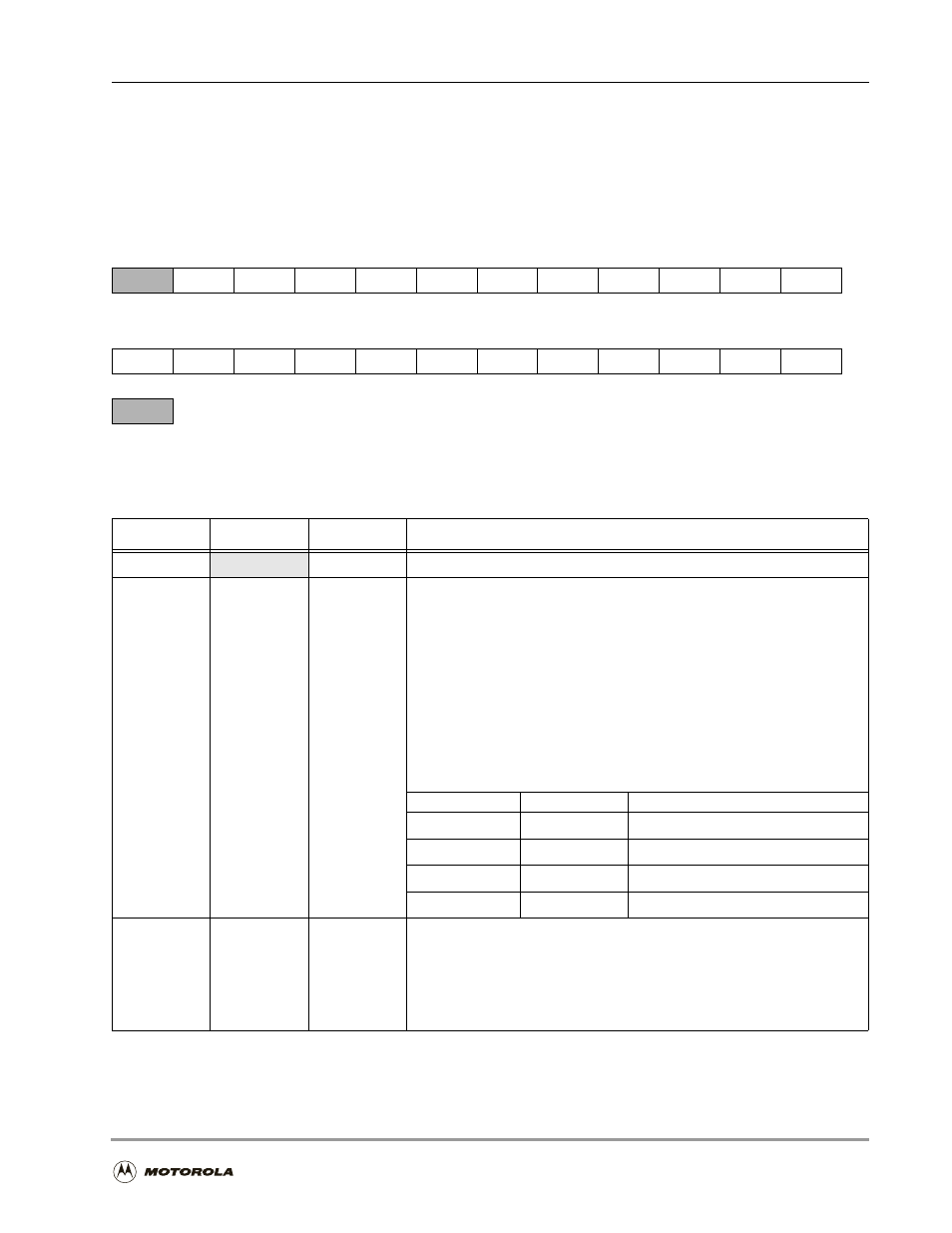

Timer Prescaler Load Register (TPLR)

The TPLR is a read/write register that controls the prescaler divide factor (that is, the number

that the prescaler counter loads and begins counting from) and the source for the prescaler

input clock.

23

22

21

20

19

18

17

16

15

14

13

12

PS1

PS0

PL20

PL19

PL18

PL17

PL16

PL15

PL14

PL13

PL12

11

10

9

8

7

6

5

4

3

2

1

0

PL11

PL10

PL9

PL8

PL7

PL6

PL5

PL4

PL3

PL2

PL1

PL0

— Reserved bit. Read as 0. Write to 0 for future compatibility

Figure 9-21. Timer Prescaler Load Register (TPLR)

Table 9-1. Timer Prescaler Load Register (TPLR) Bit Definitions

Bit Number

Bit Name

Reset Value

Description

23

0

Reserved. Write to zero for future compatibility.

22–21

PS[1–0]

0

Prescaler Source

Control the source of the prescaler clock. The prescaler’s use of a TIO

signal is not affected by the TCSR settings of the timer of the

corresponding TIO signal. If the prescaler source clock is external, the

prescaler counter is incremented by signal transitions on the TIO signal.

The external clock is internally synchronized to the internal clock. The

external clock frequency must be lower than the DSP56301 internal

operating frequency divided by 4 (that is, CLK/4).

NOTE: To ensure proper operation, change the PS[1–0] bits only when

the prescaler counter is disabled. Disable the prescaler counter by

clearing TCSR[TE] of each of three timers.

PS1

PS0

Prescaler Clock Source

0

0

Internal CLK/2

0

1

TIO0

1

0

TIO1

1

1

TIO2

20–0

PL[20–0]

0

Prescaler Preload Value

Contains the prescaler preload value, which is loaded into the prescaler

counter when the counter value reaches 0 or the counter switches state

from disabled to enabled. If PL[20–0] = N, then the prescaler counts N+1

source clock cycles before generating a prescaler clock pulse. Therefore,

the prescaler divide factor = (preload value) + 1.