Motorola DSP56301 User Manual

Page 250

SCI Programming Model

8

-14

DSP56301 User’s Manual

9

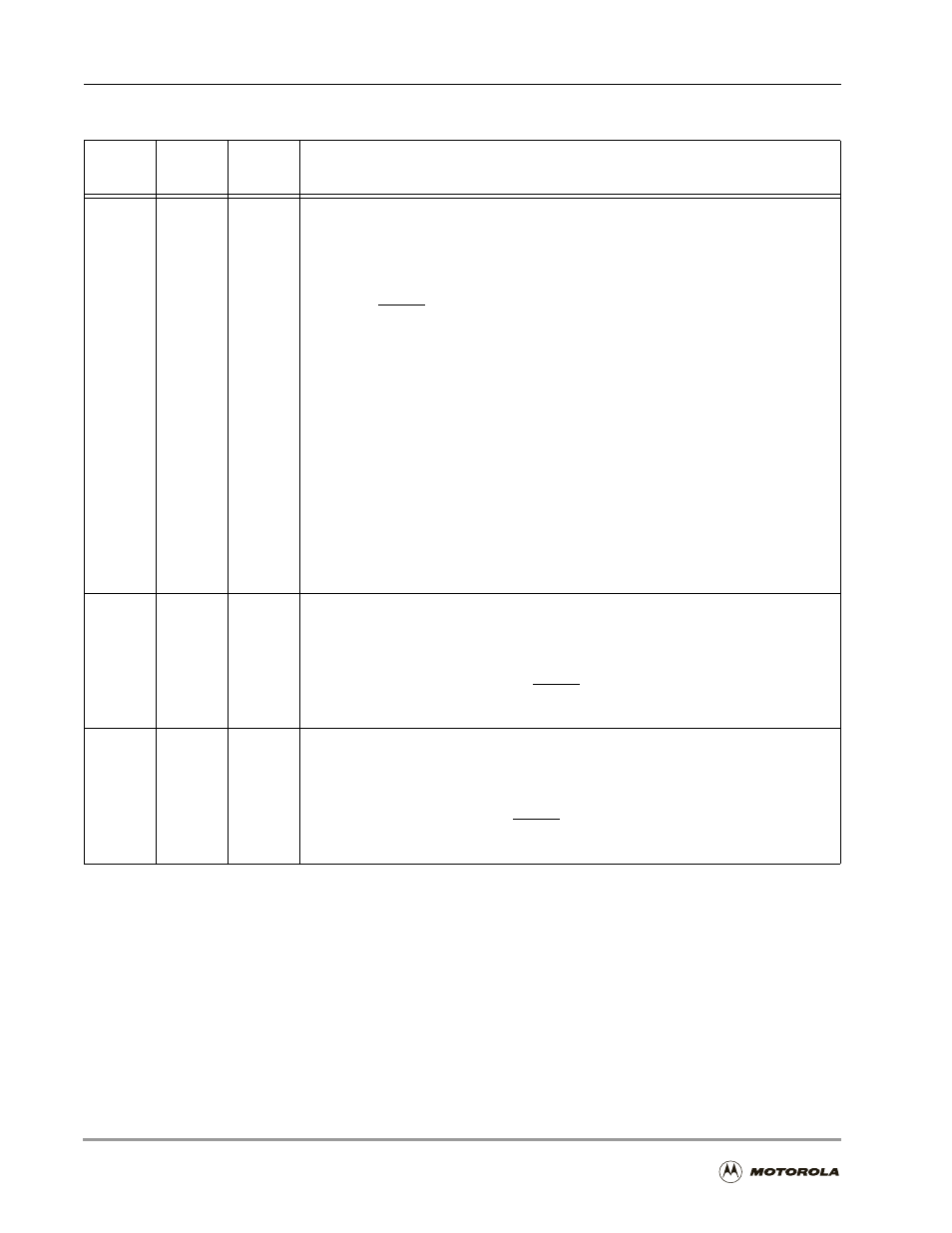

TE

0

Transmitter Enable

When TE is set, the transmitter is enabled. When TE is cleared, the transmitter

completes transmission of data in the SCI transmit data shift register, and then the

serial output is forced high (that is, idle). Data present in the SCI transmit data register

(STX) is not transmitted. STX can be written and TDRE cleared, but the data is not

transferred into the shift register. TE does not inhibit TDRE or transmit interrupts. Either

a hardware RESET signal or a software RESET instruction clears TE.

Setting TE causes the transmitter to send a preamble of 10 or 11 consecutive ones

(depending on WDS), giving you a convenient way to ensure that the line goes idle

before a new message starts. To force this separation of messages by the minimum

idle line time, we recommend the following sequence:

1.

Write the last byte of the first message to STX.

2.

Wait for TDRE to go high, indicating the last byte has been transferred to the

transmit shift register.

3.

Clear TE and set TE to queue an idle line preamble to follow immediately the

transmission of the last character of the message (including the stop bit).

4.

Write the first byte of the second message to STX.

In this sequence, if the first byte of the second message is not transferred to STX prior

to the finish of the preamble transmission, the transmit data line remains idle until STX

is finally written.

8

RE

0

Receiver Enable

When RE is set, the receiver is enabled. When RE is cleared, the receiver is disabled,

and data transfer from the receive shift register to the receive data register (SRX) is

inhibited. If RE is cleared while a character is being received, the reception of the

character completes before the receiver is disabled. RE does not inhibit RDRF or

receive interrupts. Either a hardware RESET signal or a software RESET instruction

clears RE.

7

WOMS

0

Wired-OR Mode Select

When WOMS is set, the SCI TXD driver is programmed to function as an open-drain

output and can be wired together with other TXD signals in an appropriate bus

configuration, such as a master-slave multidrop configuration. An external pullup

resistor is required on the bus. When WOMS is cleared, the TXD signal uses an active

internal pullup. Either a hardware RESET signal or a software RESET instruction

clears WOMS.

Table 8-2. SCI Control Register (SCR) Bit Definitions (Continued)

Bit

Number

Bit Name

Reset

Value

Description