Motorola DSP56301 User Manual

Page 50

Host Interface (HI32)

2

-20

DSP56301 User’s Manual

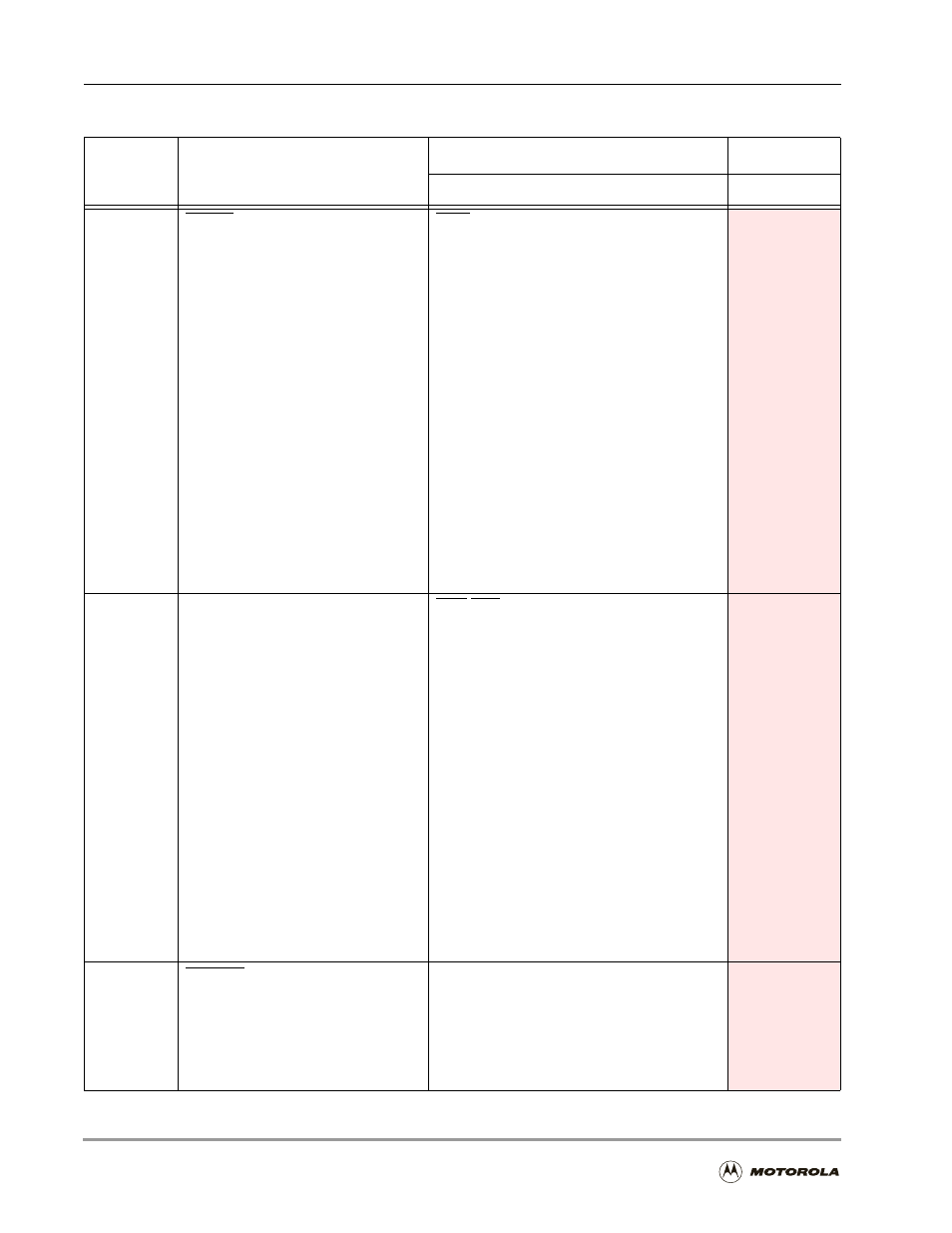

HP29

HSTOP

Host Stop

Sustained tri-state bidirectional pin.

2

Indicates that the current target is

requesting the master to stop the

current transaction.

HWR/HRW

Host Write/Read-Write

Schmitt trigger input pin.

When in the double-strobe mode of the HI32

(HDSM=0), this pin functions as host write

input strobe (HWR). The host processor

initiates a write access by asserting HWR.

Data input is latched with the rising edge of

HWR.

In the single-strobe mode of the HI32

(HDSM=1), this pin functions as host

read-write (HRW) input. It selects the direction

of data transfer for each host processor

access: from the HI32 to the host processor

when HRW is asserted and from the host

processor to the HI32 when HRW is

deasserted. The polarity of the HRW pin is

controlled by HRWP bit in the DCTR.

NOTE: Simultaneous assertion of HRD and

HWR is illegal.

disconnected

HP30

HIDSEL

Initialization Device Select

Input pin.

Used as a chip select in lieu of the

upper 21 address lines during

configuration read and write

transactions.

HRD/HDS

Host Read/Data Strobe

Schmitt-trigger input pin.

In the double-strobe mode of the HI32

(HDSM=0), this pin functions as the host read

strobe (HRD). The host processor initiates a

read access by asserting HRD. Data output

may be latched with the rising edge of HRD.

In the single-strobe mode of the HI32

(HDSM=1), this pin functions as the host data

strobe (HDS). The host processor initiates a

read access by asserting HDS with HRW

asserted. Data output may be latched with the

rising edge of HDS. The host processor

initiates a write access by asserting HDS with

HRW deasserted. Data input is latched by the

HI32 with the rising edge of HDS.

NOTE: Simultaneous assertion of HRD and

HWR is illegal.

disconnected

HP31

HFRAME

Host Cycle Frame

Sustained tri-state bidirectional pin.

2

Driven by the current master to

indicate the beginning and duration of

an access. HFRAME is deasserted in

the final data phase of the transaction.

Reserved.

Must be forced or pulled up to V

CC

.

disconnected

Table 2-12. Host Port Pins (HI32) (Continued)

Signal

Name

PCI

Universal Bus Mode

Enhanced Universal Bus Mode

GPIO