5 pll control register (pctl), Pll control register (pctl) -21, Pll control register (pctl) bit definitions -21 – Motorola DSP56301 User Manual

Page 95: 5 pll control register (pctl)

PLL Control Register (PCTL)

Core Configuration

4

-21

4.5

PLL Control Register (PCTL)

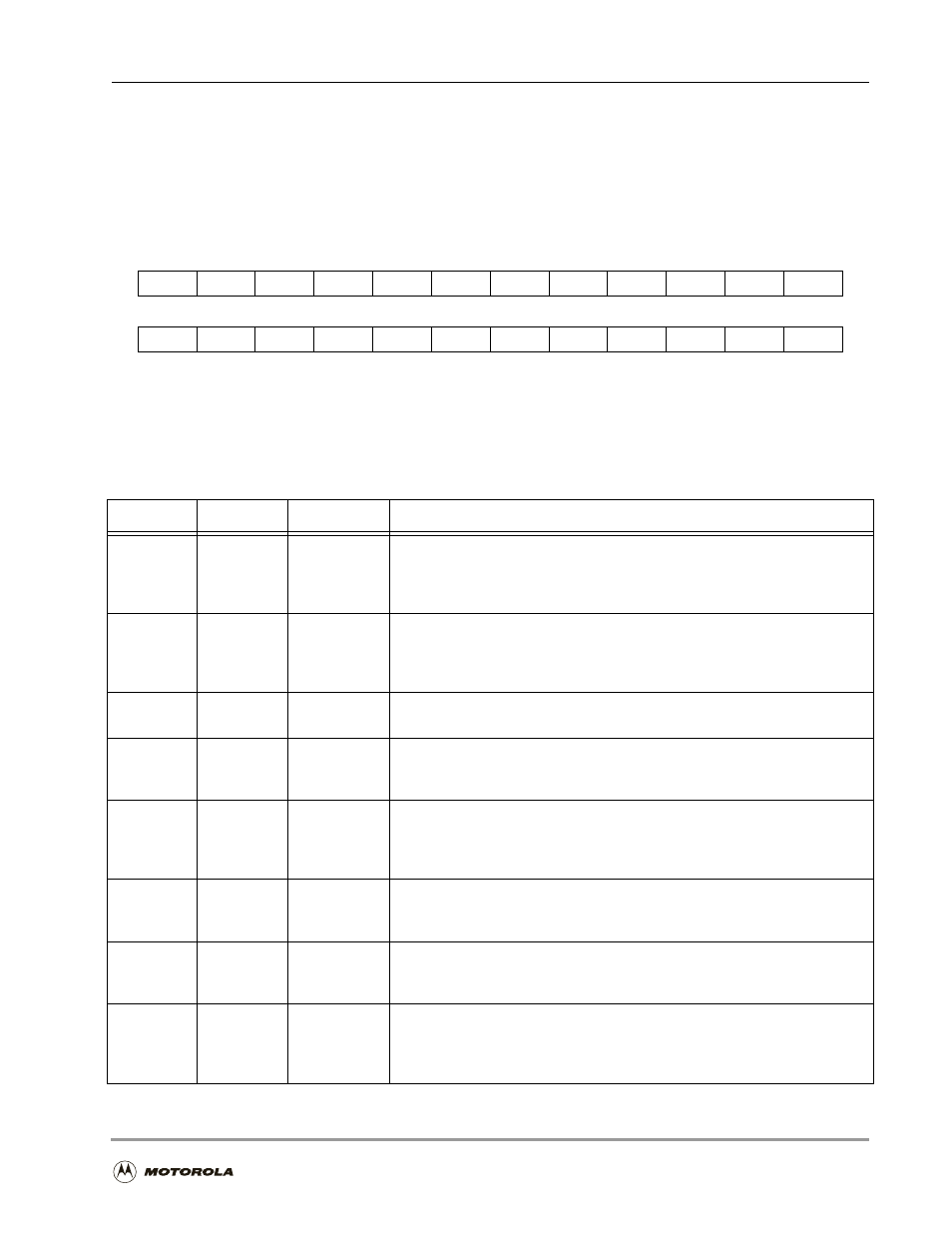

The bootstrap program must initialize the system Phase-Lock Loop (PLL) circuit by

configuring the PLL Control Register (PCTL). The PCTL is an X-I/O mapped, read/write

register that directs the on-chip PLL operation. (See Figure 4-5.)

Table 4-8 defines the DSP56301 PCTL bits. Changing the following bits may cause the PLL

to lose lock and re-lock according to the new value: PD[3–0], PEN, XTLR, and MF.

23

22

21

20

19

18

17

16

15

14

13

12

PD3

PD2

PD1

PD0

COD

PEN

PSTP

XTLD

XTLR

DF2

DF1

DF0

11

10

9

8

7

6

5

4

3

2

1

0

MF11

MF10

MF9

MF8

MF7

MF6

MF5

MF4

MF3

MF2

MF1

MF0

Figure 4-5. PLL Control Register (PCTL)

Table 4-8. PLL Control Register (PCTL) Bit Definitions

Bit Number

Bit Name

Reset Value

Description

23–20

PD[3–0]

0

Predivider Factor

Define the predivision factor (PDF) to be applied to the PLL input frequency.

The PD[3–0] bits are cleared during DSP56301 hardware reset, which

corresponds to a PDF of one.

19

COD

0

Clock Output Disable

Controls the output buffer of the clock at the CLKOUT pin. When COD is set,

the CLKOUT output is pulled high. When COD is cleared, the CLKOUT pin

provides a 50 percent duty cycle clock.

18

PEN

Set to PINIT

input value

PLL Enable

Enables PLL operation.

17

PSTP

0

PLL Stop State

Controls PLL and on-chip crystal oscillator behavior during the stop

processing state.

16

XTLD

0

XTAL Disable

Controls the on-chip crystal oscillator XTAL output. The XTLD bit is cleared

during DSP56301 hardware reset, so the XTAL output signal is active,

permitting normal operation of the crystal oscillator.

15 XTLR

0

Crystal Range

Controls the on-chip crystal oscillator transconductance. The XTLR bit is

cleared (0) during hardware reset in the DSP56303.

14–12

DF[2–0]

0

Division Factor

Define the DF of the low-power divider. These bits specify the DF as a power

of two in the range from 2

0

to 2

7

.

11–0

MF[11–0]

0

PLL Multiplication Factor

Define the multiplication factor that is applied to the PLL input frequency. The

MF bits are cleared during DSP56301 hardware reset and thus correspond to

an MF of one.