Motorola DSP56301 User Manual

Page 221

ESSI Programming Model

Enhanced Synchronous Serial Interface (ESSI)

7

-23

4

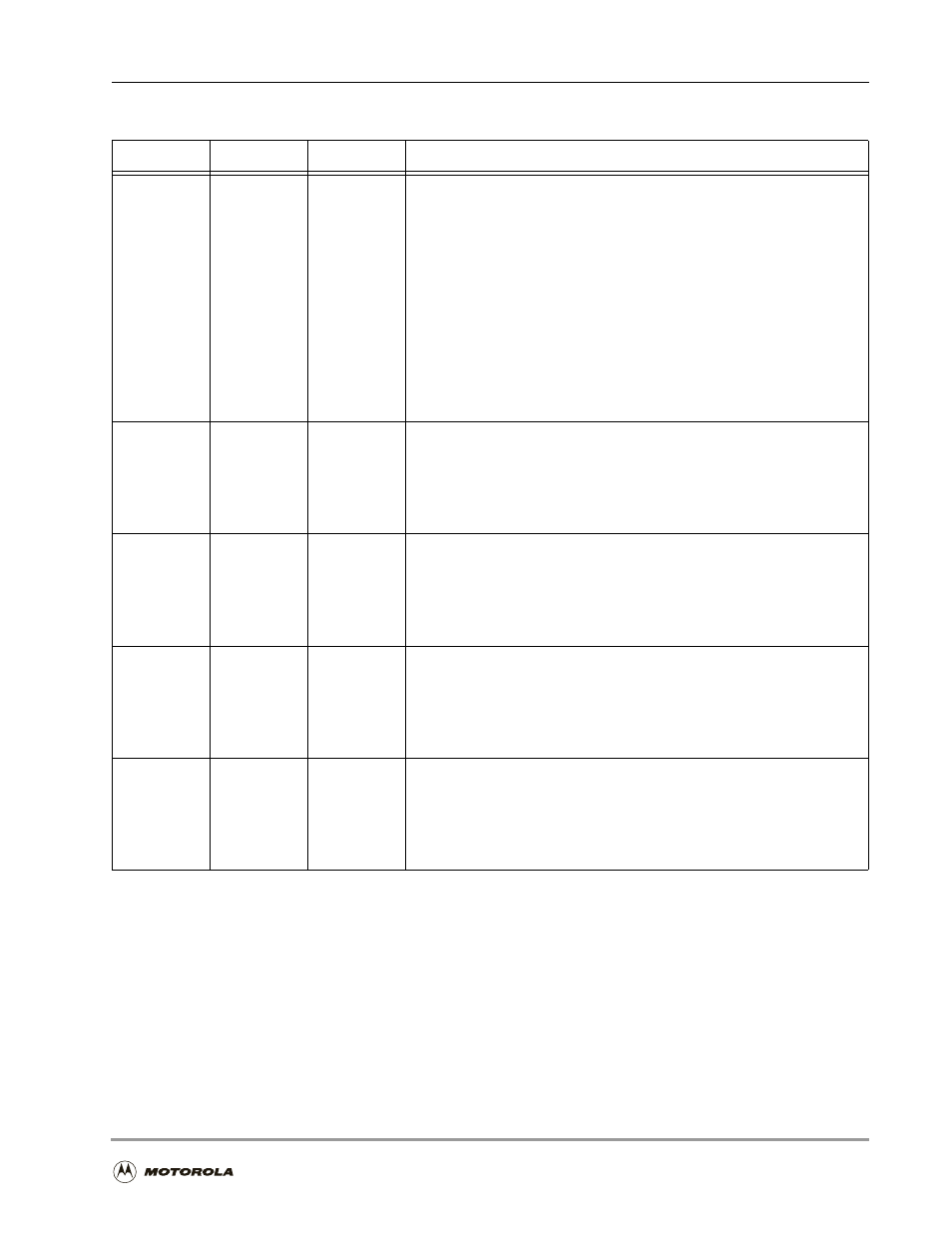

SCD2

0

Serial Control Direction 2

Controls the direction of the SC2 I/O signal. When SCD2 is set, SC2 is an

output; when SCD2 is cleared, SC2 is an input.

Note:

Programming the ESSI to use an internal frame sync (that is,

SCD2 = 1 in CRB) causes the SC2 and SC1 signals to be

programmed as outputs. However, if the corresponding

multiplexed pins are programmed by the Port Control Register

(PCR) to be GPIOs, the GPIO Port Direction Register (PRR)

chooses their direction. The ESSI uses an external frame sync if

GPIO is selected. To assure correct operation, either program

the GPIO pins as outputs or configure the pins in the PCR as

ESSI signals. The default selection for these signals after reset is

GPIO. This note applies to both ESSI0 and ESSI1.

3

SCD1

0

Serial Control Direction 1

In Synchronous mode (SYN = 1) when transmitter 2 is disabled (TE2 = 0),

or in Asynchronous mode (SYN = 0), SCD1 controls the direction of the

SC1 I/O signal. When SCD1 is set, SC1 is an output; when SCD1 is

cleared, SC1 is an input. When TE2 is set, the value of SCD1 is ignored

and the SC1 signal is always an output.

2

SCD0

0

Serial Control Direction 0

In Synchronous mode (SYN = 1) when transmitter 1 is disabled (TE1 = 0),

or in Asynchronous mode (SYN = 0), SCD0 controls the direction of the

SC0 I/O signal. When SCD0 is set, SC0 is an output; when SCD0 is

cleared, SC0 is an input. When TE1 is set, the value of SCD0 is ignored

and the SC0 signal is always an output.

1 OF1 0

Serial Output Flag 1

In Synchronous mode (SYN = 1), when transmitter 2 is disabled (TE2 = 0),

the SC1 signal is configured as ESSI flag 1. When SCD1 is set, SC1 is an

output. Data present in bit OF1 is written to SC1 at the beginning of the

frame in Normal mode or at the beginning of the next time slot in Network

mode.

0

OF0

0

Serial Output Flag 0

In Synchronous mode (SYN = 1), when transmitter 1 is disabled (TE1 = 0),

the SC0 signal is configured as ESSI flag 0. When SCD0 is set, the SC0

signal is an output. Data present in Bit OF0 is written to SC0 at the

beginning of the frame in Normal mode or at the beginning of the next time

slot in Network mode.

Table 7-4. ESSI Control Register B (CRB) Bit Definitions (Continued)

Bit Number

Bit Name

Reset Value

Description