16 x serial clock -21 – Motorola DSP56301 User Manual

Page 257

SCI Programming Model

Serial Communication Interface (SCI)

8

-21

As noted in Section 8.6.1, the SCI can be configured to operate in a single Synchronous mode

or one of five Asynchronous modes. Synchronous mode requires that the TX and RX clocks

use the same source, but that source may be the internal SCI clock if the SCI is configured as

a master device or an external clock if the SCI is configured as a slave device. Asynchronous

modes may use clocks from the same source (internal or external) or different sources for the

TX clock and the RX clock.

For synchronous operation, the SCI uses a clock that is equal to the two times the desired bit

rate (designated as the 2

×

clock) for both internal and external clock sources. It must use the

same source for both the TX and RX clock. The internal clock is used if the SCI is the master

device and the external clock is used if the SCI is the slave device, as noted above. The clock

is gated and limited to a maximum frequency equal to one eighth of the DSP core operating

frequency (that is, 12.5 MHz for a DSP core frequency of 100 MHz).

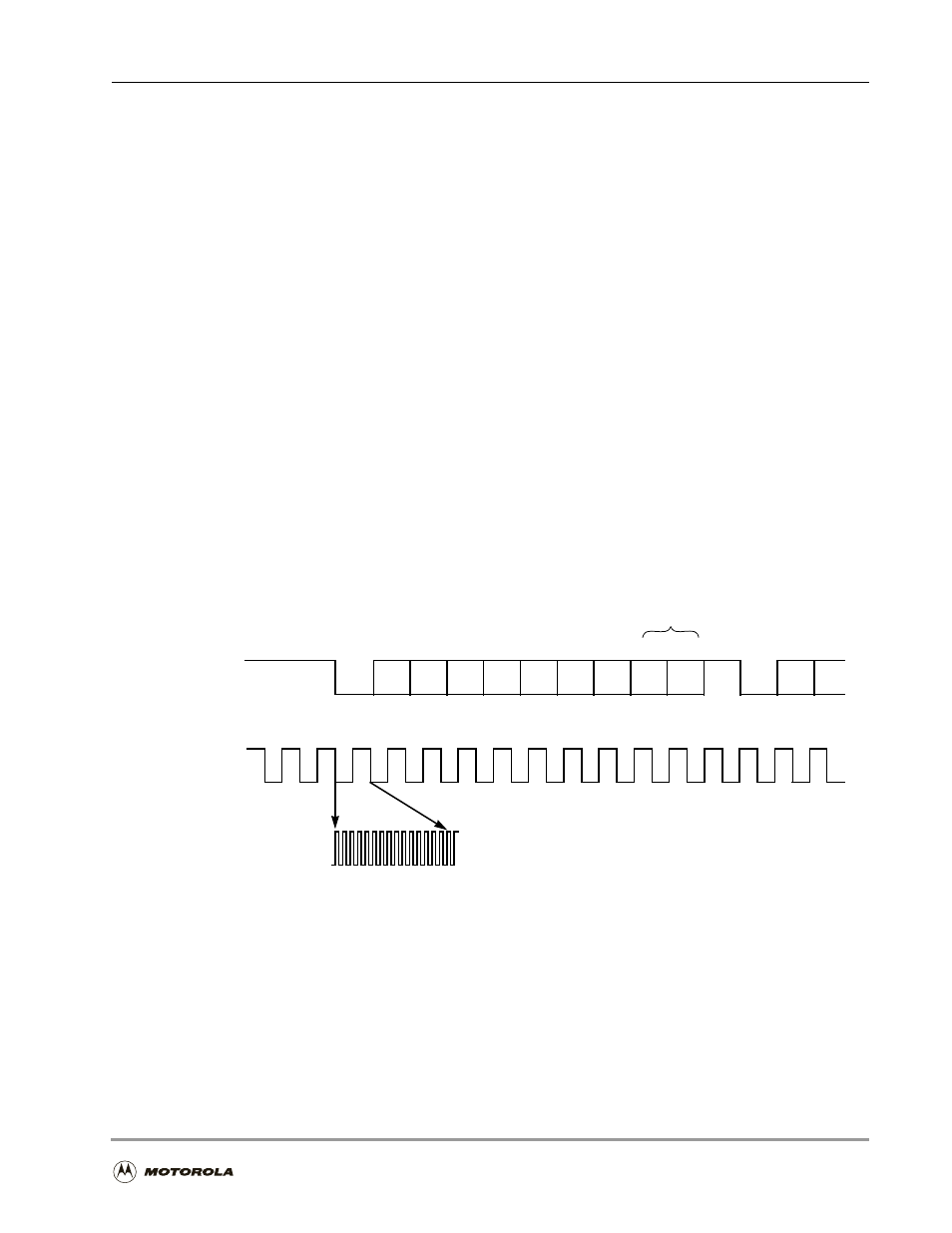

For asynchronous operation, the SCI can use the internal and external clocks in any

combination as the source clocks for the TX clock and RX clock. If an external clock is used

for the

SCLK

input, it must be sixteen times the desired bit rate (designated as the 16

×

clock),

as indicated in Figure 8-6. When the internal clock is used to supply a clock to an external

device, the clock can use the actual bit rate (designated as the 1

×

clock) or the 16

×

clock

rate, as determined by the COD bit. The output clock is continuous.

When SCKP is cleared, the transmitted data on the

TXD

signal changes on the negative edge

of the serial clock and is stable on the positive edge. When SCKP is set, the data changes on

the positive edge and is stable on the negative edge. The received data on the

RXD

signal is

sampled on the positive edge (if SCKP = 0) or on the negative edge (if SCKP = 1) of the

serial clock.

Figure 8-6. 16 x Serial Clock

RX, TX Data

(SSFTD = 0)

Idle Line

Start

Select 8-or 9-bit Words

x1 Clock

x16 Clock

(SCKP = 0)

1

0

2

3

4

5

6

7

8

Stop

Start