Sci baud rate generator -20 – Motorola DSP56301 User Manual

Page 256

SCI Programming Model

8

-20

DSP56301 User’s Manual

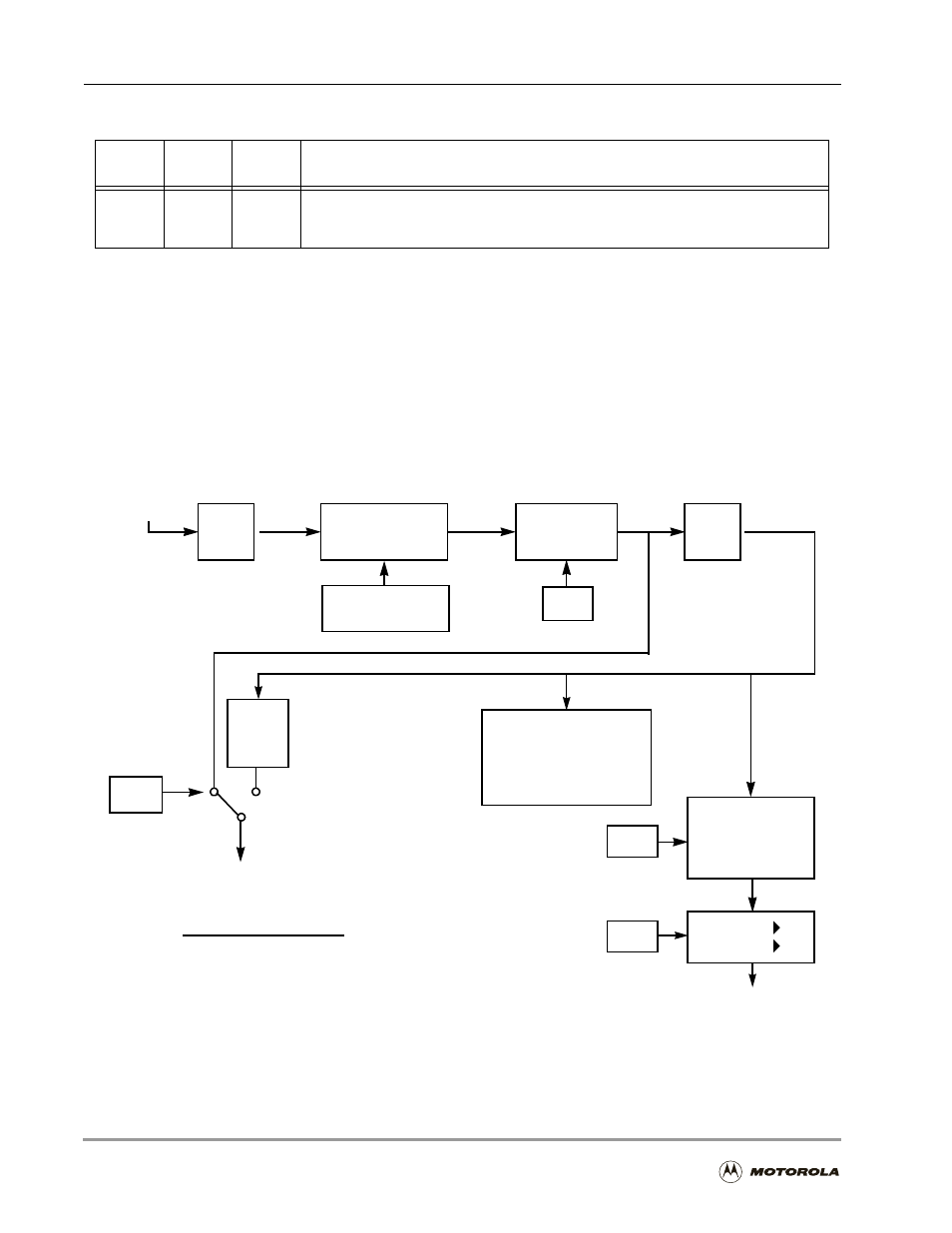

The SCI clock determines the data transmission (baud) rate and can also establish a periodic

interrupt that can act as an event timer or be used in any other timing function. Bits CD11–

CD0, SCP, and SCR[STIR] work together to determine the time base. If SCR[TMIE] = 1

when the periodic time-out occurs, the SCI timer interrupt is recognized and pending. The

SCI timer interrupt is automatically cleared when the interrupt is serviced. This interrupt

occurs every time the periodic timer times out.

Figure 8-5 shows the block diagram of the internal clock generation circuitry with the

formula to compute the bit rate when the internal clock is used.

11–0

CD[11–0]

0

Clock Divider

Specifies the divide ratio of the prescale divider in the SCI clock generator. A divide

ratio from 1 to 4096 (CD[11–0] = $000 to $FFF) can be selected.

Figure 8-5. SCI Baud Rate Generator

Table 8-5. SCI Clock Control Register (SCCR) Bit Definitions (Continued)

Bit

Number

Bit Name

Reset

Value

Description

F

core

Divide

By 2

12-bit Counter

Prescaler:

Divide by

1 or 8

Internal Clock

SCI Core Logic

Uses Divide by 16 for

Asynchronous

Uses Divide by 2 for

Synchronous

COD

SCKP

If Asynchronous

Divide by 1 or 16

If Synchronous

Divide By 2

SCLK

Divide

By 2

Divide

by 16

Timer

Interrupt

(STMINT)

Fcore

bps = 64

×

(7(SCP) + 1)

×

CD + 1)

where: SCP = 0 or 1

CD = $000 to $FFF

STIR

SCKP = 0 +

SCKP = 1 -

CD[11–0]

SCP