B-16, Figure b-16, Status/command configuration register (cstr/ccmr) – Motorola DSP56301 User Manual

Page 340: Host processor (hi32)

Programming Sheets

B

-28

DSP56301 User’s Manual

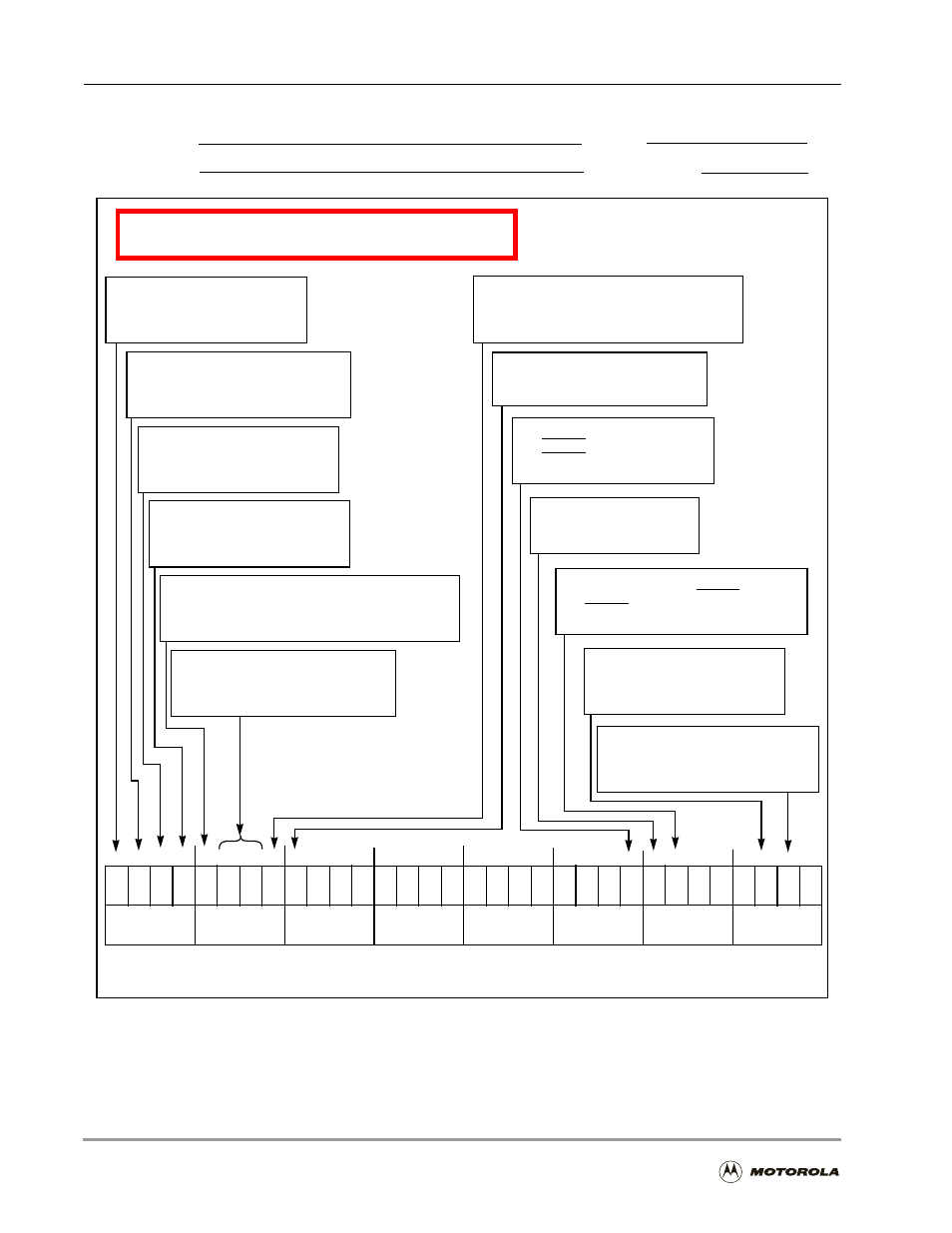

Figure B-16. Status/Command Configuration Register (CSTR/CCMR)

Host Processor (HI32)

HI32 Status/Command Configuration Register (CSTR/CCMR)

Reset = $02400000

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

0

19 18 17 16

23 22 21 20

*

= Reserved, Program as 0

*

0

Read/Write

Application:

Date:

Programmer:

Sheet 7 of 10

27 26 25 24

31 30 29 28

*

0

*

0

*

0

*

0

*

0

*

0

*

0

*

0

*

0

*

0

RTA

WCC PERR

DPE

SSE

RMA

BM

MSE

*

0

*

0

*

0

*

0

*

0

*

0

*

0

SERE

STA

DST1 DST0 DPR

FBBC

Detected Parity Error, Bit 31

0 = No parity error detected

1 = Parity error detected

Modes: PCI only

Signaled System Error, Bit 30

0 = No signaled system error detected

1 = Signaled system error detected

Modes: PCI only

Received Master Abort, Bit 29

0 = No master abort received

1 = Master abort bus state

Modes: PCI only

Received Target Abort, Bit 28

0 = No target abort received

1 = Target abort received

Modes: PCI only

Signalled Target Abort, Bit 27

0 = No target abort issued (HI32 as target)

1 = HI32 issued target abort to terminate transaction

Modes: PCI only

DEVSEL Timing, Bits 26–25

Always $1 (hardwired)

HI32 is medium DEVSEL timing class

Modes: PCI only

Data Parity Reported, Bit 24

0 = No parity error reported

1 = HI32 (as master) reported data parity error

Modes: PCI only

Fast Back-to-Back Capable, Bit 23

Always 1 (hardwired)

Modes: PCI only

System Error Enable, Bit 8

0 = HSERR pin disabled

1 = HSERR pin enabled

Modes: PCI only

Write Cycle Control, Bit 7

Always 0 (hardwired)

Modes: PCI only

Parity Error Response, Bit 6

0 = HI32 does not drive HPERR

1 = HPERR enabled for driving or detection

Modes: PCI only

Bus Master Enable, Bit 2

0 = HI32 bus mastership disabled

1 = HI32 bus mastership enabled

Modes: PCI only

Memory Space Enable, Bit 1

0 = Memory space response disabled

1 = Memory space response enabled

Modes: PCI only

0 1

1

0