Motorola DSP56301 User Manual

Page 191

Host-Side Programming Model

Host Interface (HI32)

6

-73

6.8.13

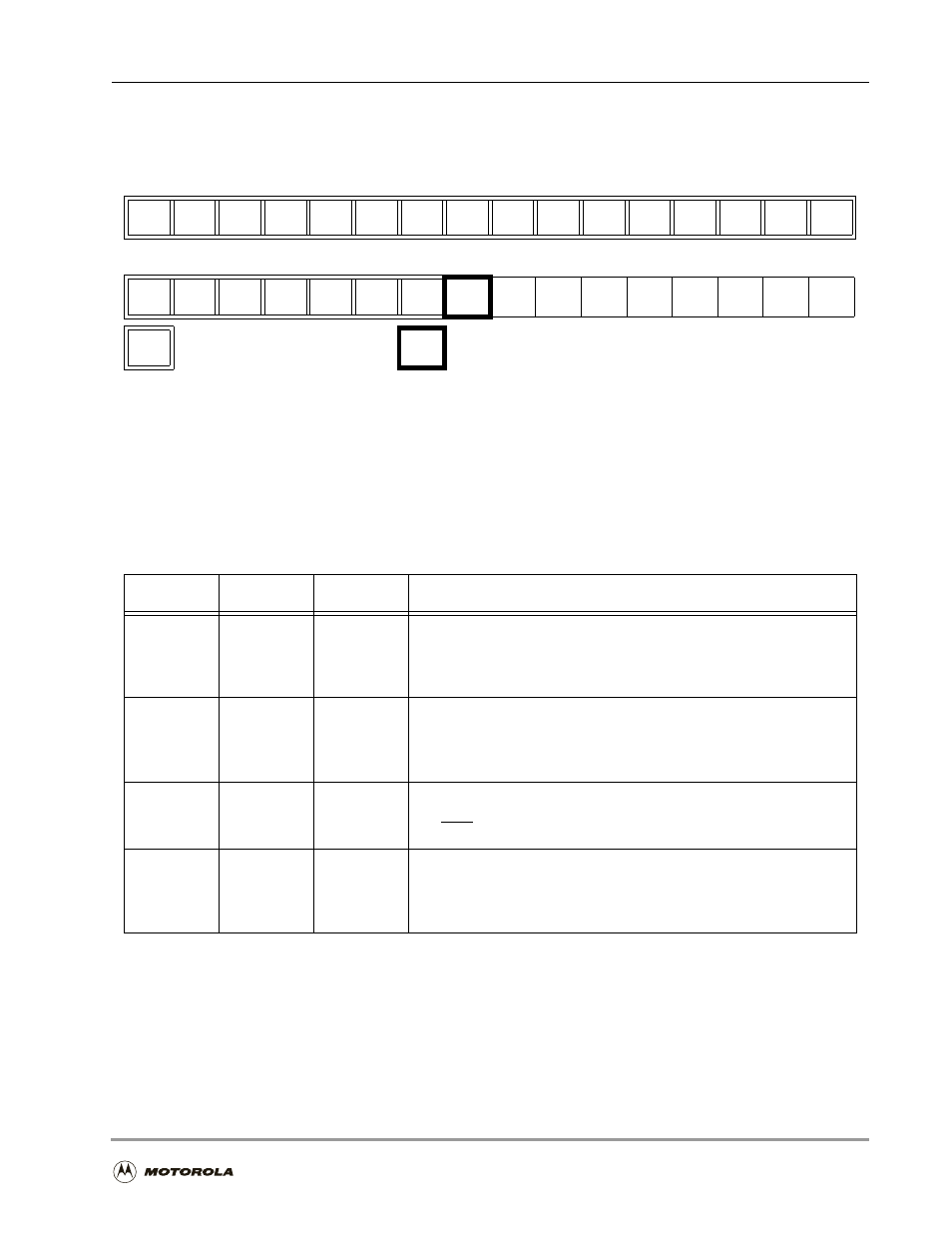

Interrupt Line-Interrupt Pin Configuration Register(CILP)

CILP is PCI-standard read-only register mapped into the PCI configuration space in PCI

mode or in mode 0 (HM

=

$1 or $0). CILP is accessed when a configuration read command is

in progress and the PCI address is $FC. The DSP56300 core cannot access CILP. The host

can access CILP only in PCI mode (HM

≠

$1). The 24 most significant bits of the CILP

register are hardwired and are unaffected by any type of reset.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

ML7

ML6

ML5

ML4

ML3

ML2

ML1

ML0

MG7

MG6

MG5

MG4

MG3

MG2

MG1

MG0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

IP7

IP6

IP5

IP4

IP3

IP2

IP1

IP0

IL7

IL6

IL5

IL4

IL3

IL2

IL1

IL0

Hardwired to zero

Hardwired to one

Figure 6-22. Interrupt Line-Interrupt Pin Configuration Register(CILP)

Table 6-30. Interrupt Line-Interrupt Pin Configuration Register(CILP) Bit Definitions

Bit Number

Bit Name

Reset Value

Description

31–24

ML[7–0]

0 (Hardwired) MAX_LAT

Specifies how often the device needs to gain access to the PCI bus.

Because the HI32 has no major requirements for the settings of Latency

Timers, these bits are hardwired to zero.

23–16

MG[7–0]

0 (Hardwired) MIN_GNT

Specifies how long a burst the device needs. Because the HI32 has no

major requirements for the settings of Latency Timers, these bits are

hardwired to zero.

15–8

IP[7–0]

1 (Hardwired) Interrupt Pin

Specifies which interrupt the device uses. A value of 1 corresponds to

PCI INTA.

7–0

IL[7–0]

0

Interrupt Line

Communicates PCI interrupt line routing information. POST software

writes the routing information into these bits as it initializes and

configures the PCI system.