Summary of hi32 signals and modes -14, Table 2-11, Table 2-10. host interface (continued) – Motorola DSP56301 User Manual

Page 44

Host Interface (HI32)

2

-14

DSP56301 User’s Manual

HAD[31–16]

HD[23–8]

Input/Output

Input/Output

Tri-stated

Host Address/Data 16–31—When the HI32 is programmed to

interface with a PCI bus and the HI function is selected, these

signals are lines 16–31 of the bidirectional, multiplexed

Address/Data bus.

Host Data 8–23—When the HI32 is programmed to interface with a

universal non-PCI bus and the HI function is selected, these signals

are lines 8–23 of the bidirectional Data bus.

Port B —When the HI32 is configured as GPIO through the DCTR,

these signals are internally disconnected.

HRST

HRST

Input

Input

Tri-stated

Hardware Reset—When the HI32 is programmed to interface with

a PCI bus and the HI function is selected, this is the Hardware Reset

input.

Hardware Reset—When the HI32 is programmed to interface with

a universal non-PCI bus and the HI function is selected, this signal

is the Hardware Reset Schmitt-trigger input.

Port B —When the HI32 is configured as GPIO through the DCTR,

this signal is internally disconnected.

HINTA

Output, open

drain

Tri-stated

Host Interrupt A—When the HI function is selected, this signal is

the Interrupt A open-drain output.

Port B —When the HI32 is configured as GPIO through the DCTR,

this signal is internally disconnected.

PVCL

Input

Input

PCI Voltage Clamp—When the HI32 is programmed to interface

with a PCI bus and the HI function is selected and the PCI bus uses

a 3 V signal environment, connect this pin to V

CC

(3.3 V) to enable

the high voltage clamping required by the PCI specifications. In all

other cases, including a 5 V PCI signal environment, leave the input

unconnected.

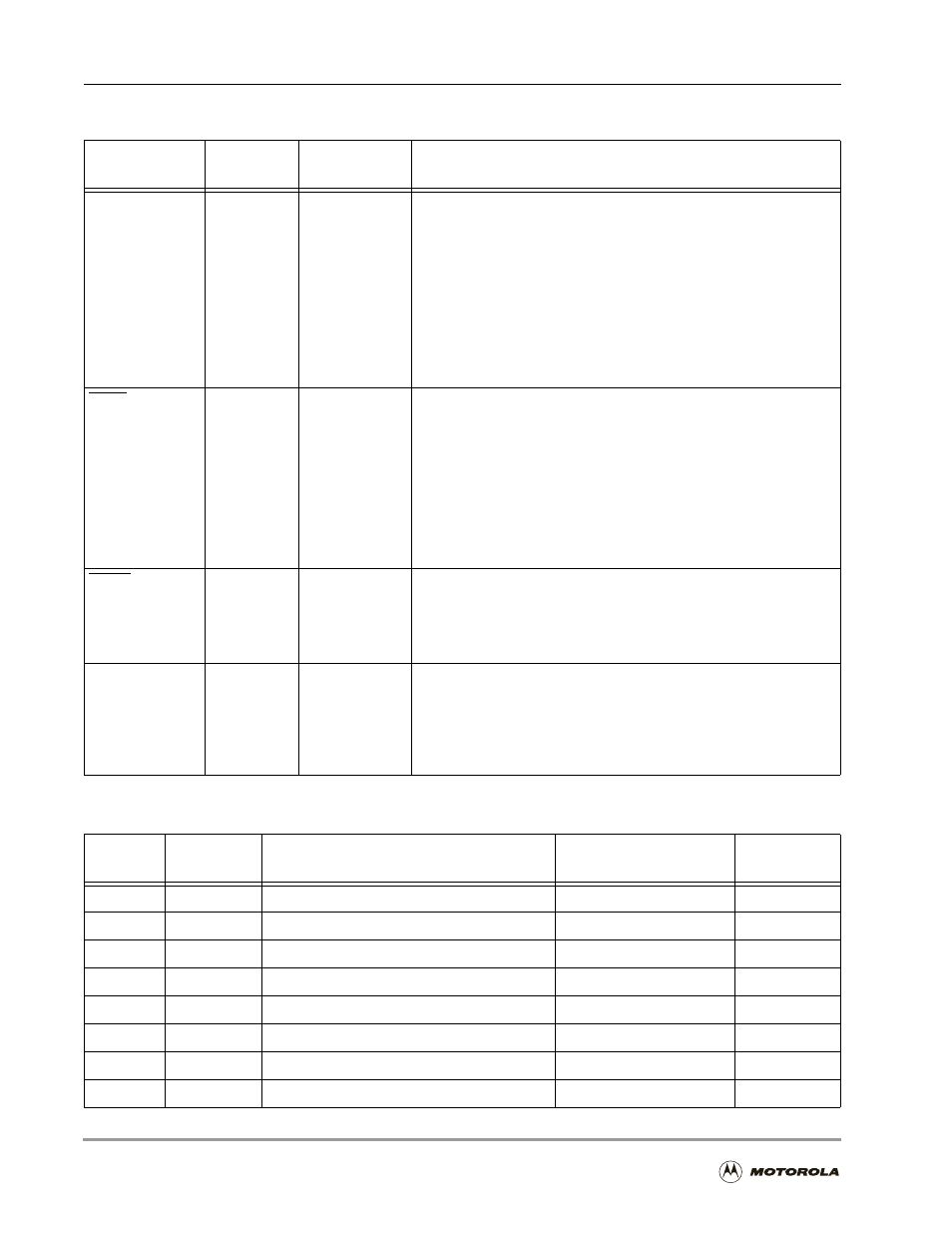

Table 2-11. Summary of HI32 Signals and Modes

Signal

Name

PCI Mode

Enhanced Universal Bus Mode

Universal Bus Mode

GPIO Mode

HP0

HAD0

HA3

HIO0

HP1

HAD1

HA4

HIO1

HP2

HAD2

HA5

HIO2

HP3

HAD3

HA6

HIO3

HP4

HAD4

HA7

HIO4

HP5

HAD5

HA8

HIO5

HP6

HAD6

HA9

HIO6

HP7

HAD7

HA10

HIO7

Table 2-10. Host Interface (Continued)

Signal Name

Type

State During

Reset

Signal Description