10 dsp host port gpio direction register (dirh), 11 dsp host port gpio data register (dath), Dsp host port direction register (dirh) -43 – Motorola DSP56301 User Manual

Page 161: Dsp host port gpio data register (dath) -43, Dath and dirh functionality -43, 10 dsp host port gpio direction register (dirh), 11 dsp host port gpio data register (dath)

HI32 DSP-Side Programming Model

Host Interface (HI32)

6

-43

6.7.10

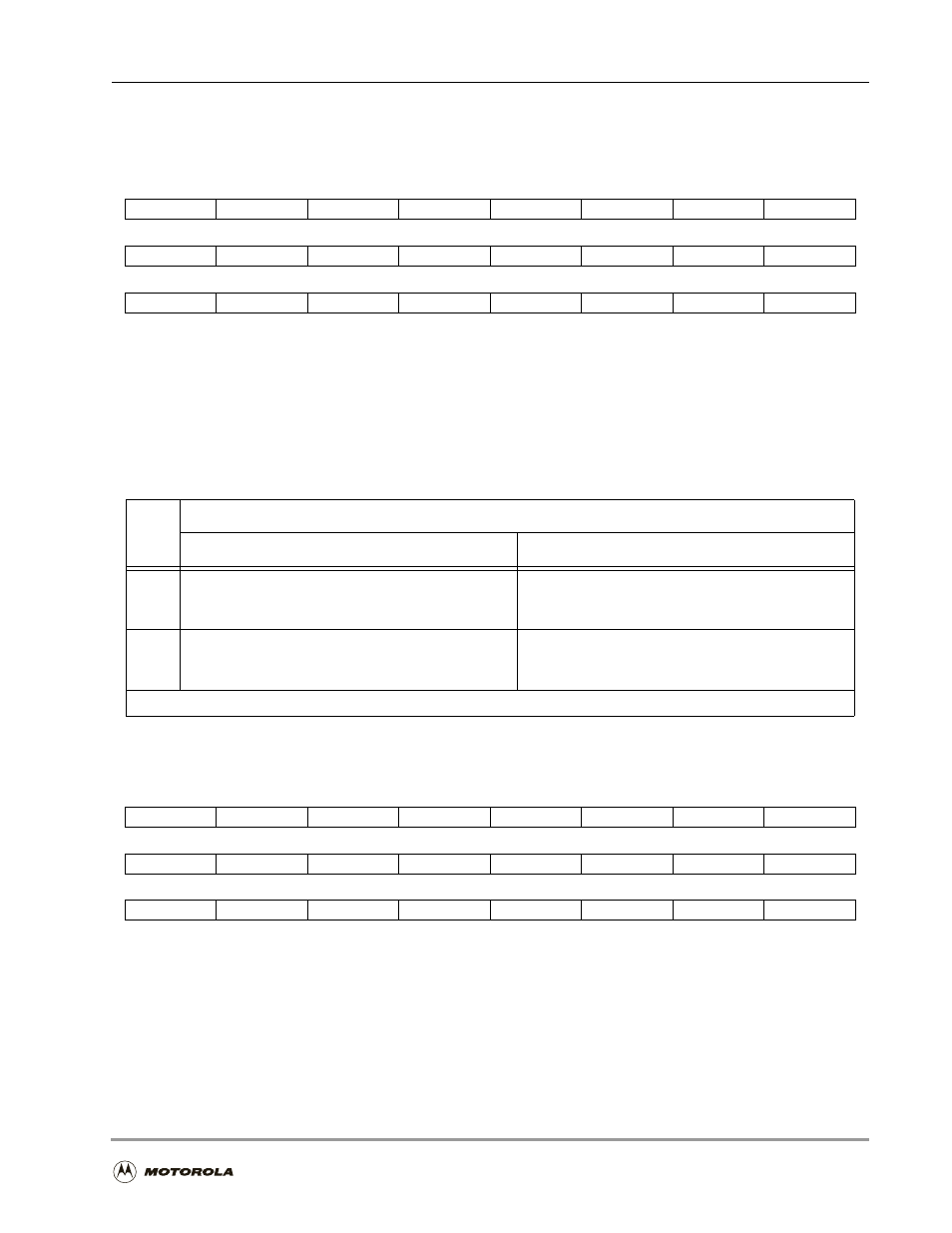

DSP Host Port GPIO Direction Register (DIRH)

A 24-bit read/write register by which the DSP56300 core controls the direction of the host

port pins in GPIO mode. The host processor cannot access DIRH. The DIR[23–0] bits define

the corresponding GPIO pins as input or output. The functionality of DIR[23–0] is defined in

Table 6-16. Hardware and software resets clear all DIRH bits.

6.7.11

DSP Host Port GPIO Data Register (DATH)

A 24-bit read/write data register by which the DSP56300 core reads or writes data to/from

host port pins configured as GPIO. The host processor cannot access DATH. DAT[23– 0]

read or write data from/to the corresponding GPIO pin. The functionality of the

DAT[23–0] bits is defined in Table 6-16. Hardware and software resets clear all DATH bits.

23

22

21

20

19

18

17

16

DIR23

DIR22

DIR21

DIR20

DIR19

DIR18

DIR17

DIR16

15

14

13

12

11

10

9

8

DIR15

DIR14

DIR13

DIR12

DIR11

DIR10

DIR9

DIR8

7

6

5

4

3

2

1

0

DIR7

DIR6

DIR5

DIR4

DIR3

DIR2

DIR1

DIR0

Figure 6-11. DSP Host Port Direction Register (DIRH)

Table 6-16. DATH and DIRH Functionality

DIRx

DATx

GPIO Pin

1

Non-GPIO Pin

1

0

Read-only bit. The value read is the binary value of

the pin. The corresponding pin is configured as an

input.

Read-only bit. Does not contain significant data.

1

Read/write bit. The value written is the value read.

The corresponding pin is configured as an output,

and is driven with the data written to DATx.

Read/write bit. The value written is the value read.

Note:

1.

Defined by the selected mode

23

22

21

20

19

18

17

16

DAT23

DAT22

DAT21

DAT20

DAT19

DAT18

DAT17

DAT16

15

14

13

12

11

10

9

8

DAT15

DAT14

DAT13

DAT12

DAT11

DAT10

DAT9

DAT8

7

6

5

4

3

2

1

0

DAT7

DAT6

DAT5

DAT4

DAT3

DAT2

DAT1

DAT0

Figure 6-12. DSP Host Port GPIO Data Register (DATH)